Ваш город: Москва

Блиц-обзор памяти High Bandwidth Memory

Введение

Компания Micron больше двух лет рассказывает о преимуществах новой высокоскоростной памяти Hybrid Memory Cube (HMC). Впрочем, она не только о ней рассказывает, но и готовит второе поколение HMC с максимальной скоростью 30 Гбит/с на каждую линию интерфейса, что вдвое выше скорости обмена для первой версии спецификаций HMC. Первое поколение 2-ГБ микросхем памяти HMC Micron с прошлой осени поставляется клиентам компании, а компания Altera, к примеру, уже подготовила к выпуску SoC со встроенным контроллером памяти HMC. Однако память Micron Hybrid Memory Cube — это лишь частный случай так называемой «широкополосной» памяти High Bandwidth Memory (HBM DRAM).

Готовность стандарта и начало поставок образцов HBM DRAM

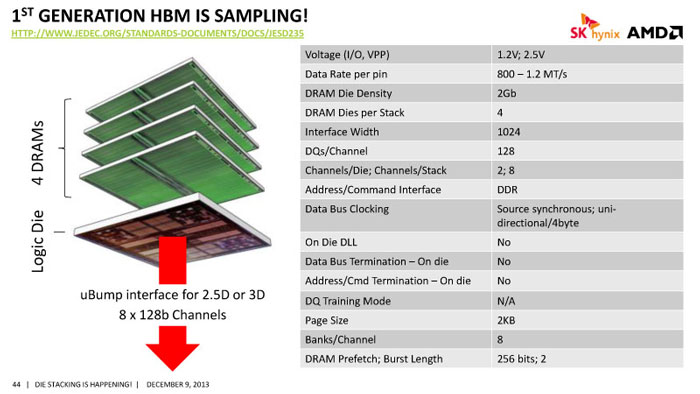

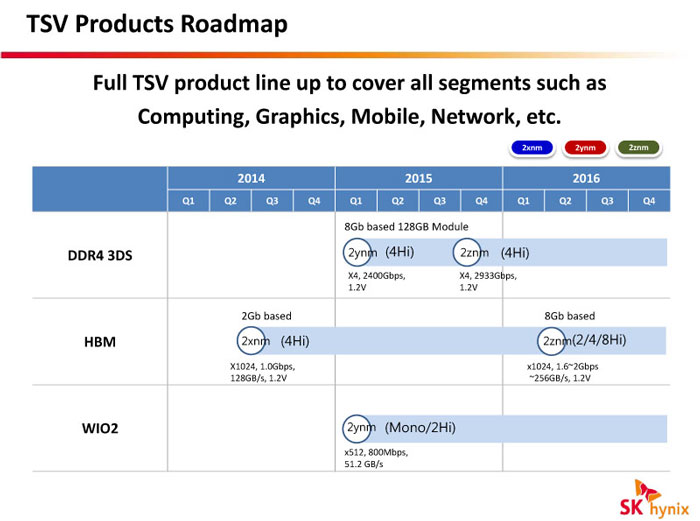

Стандарт памяти HBM разрабатывает комитет JEDEC. Официально близкая к чистовой редакции версия стандарта JESD235 была представлена рабочей группой комитета в феврале этого года на конференции IEEE International Solid-State Circuits Conference, но это не мешает компании SK Hynix выпускать образцы памяти HBM, основываясь на предварительных спецификациях. Впрочем, стандарт JESD235 достаточно гибкий, что не противоречит сосуществованию памяти HMC и HBM. На днях компания SK Hynix начала поставки 8-Гбит образцов памяти HBM (четыре 2-Гбит кристалла в стеке). Массовое производство микросхем HBM DRAM запланировано на вторую половину текущего года, а в составе продукции они появятся в 2015 году. Собственно, готовность компании SK Hynix приступить к массовым поставкам HBM DRAM и стало причиной для появления этой небольшой статьи, в которой мы попытаемся собрать воедино основную информацию о возможностях новой памяти. А чтобы было интереснее, напомним, что о намерении использовать память HBM компании SK Hynix в составе будущих видеокарт уже заявили компании AMD и NVIDIA.

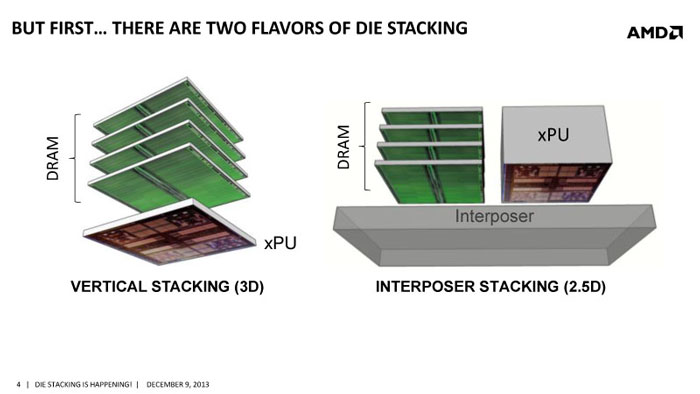

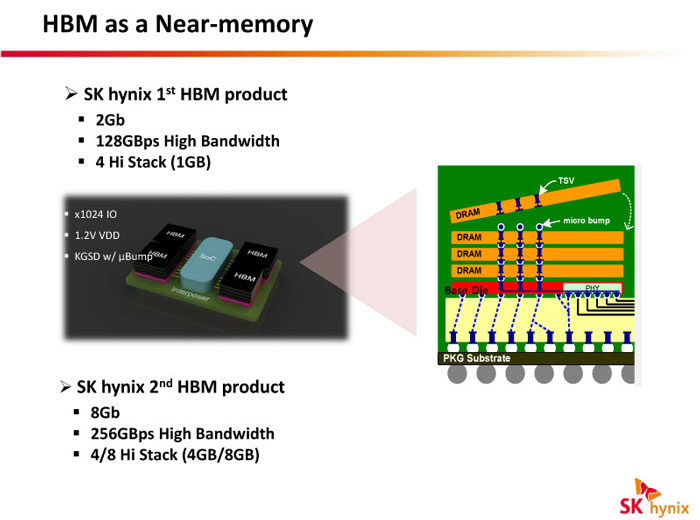

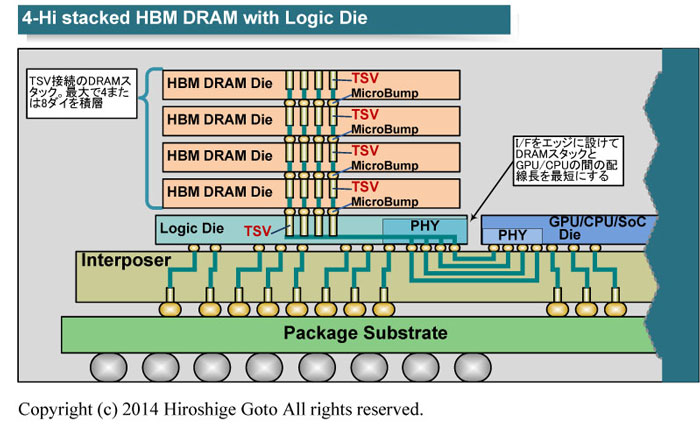

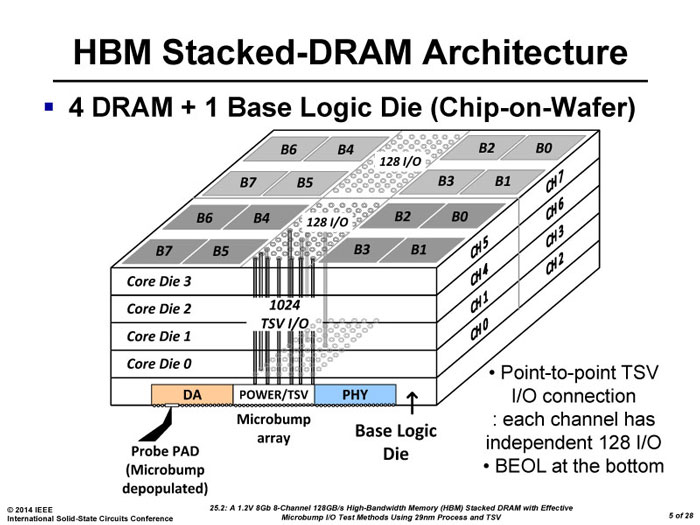

Как и память Hybrid Memory Cub, память High Bandwidth Memory представляет собой стековую компоновку из четырёх кристаллов DRAM с интерфейсом DDR и контроллера памяти. Между собой кристаллы в стеке соединяются с помощью контактных групп u-Bump, которые являются продолжением сквозных металлизированных TSVs-соединений, пронизывающих каждый кристалл. За счёт использования TSVs отпадает необходимость в проводной обвязке с вышележащими кристаллами, что делает решение предельно компактным по площади. Также метод TSVs даёт возможность расположить стек из памяти непосредственно на центральном процессоре или на графическом процессоре (как вариант, стек можно расположить на одной подложке с CPU или GPU — это так называемая 2,5D упаковка). «Чистая» 3D-упаковка — это когда CPU и GPU имеют в своём составе TSVs-металлизацию и, соответственно, выносную контактную группу как продолжение TSVs для прямого соединения со стеком памяти.

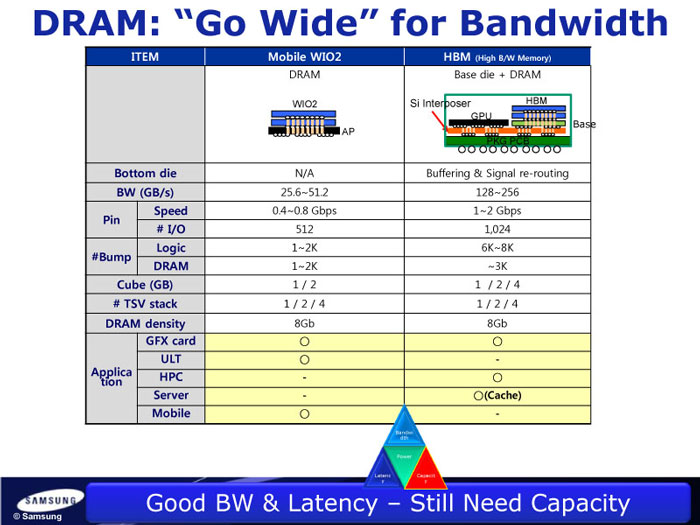

Ширина интерфейса HBM DRAM равна 1024 бит, что при скорости в первом поколении 1-2 Гбит/с на контакт даёт пропускную способность сборки на уровне 128-256 ГБ/с. В этом плане память HBM пошла дальше памяти Wide I/O и Wide I/O 2, тоже представляющей собой новый стандарт памяти с расширенным интерфейсом, но который ограничен шириной шины в 512 бит. Память Wide I/O будет использоваться в мобильных устройствах как некая альтернатива HBM, тогда как память HBM пропишется в суперкомпьютерах, видеокартах и в сетевом оборудовании. Также следует обратить внимание, что память Wide I/O 2 планируется выпускать сразу в одном стеке с прикладным процессором в виде TSVs 3D-упаковки, тогда как память HBM DRAM на первых порах будет компоноваться с CPU или GPU в виде 2,5D-упаковки (с использованием TSVs и общей подложки). Это значительно ускорит появление решений NVIDIA и AMD с использованием памяти HBM DRAM. Кроме того, проблему отвода тепла от процессора никто не отменял. «Поджаривать» память — это не лучший вариант заботы о стабильности работы системы. Наконец, если говорить о развитии HBM по отношению к Wide I/O 2, то в последующих поколениях стандарта скорость обмена по интерфейсу HBM увеличится до 512 ГБ/с и даже до 1 ТБ/с.

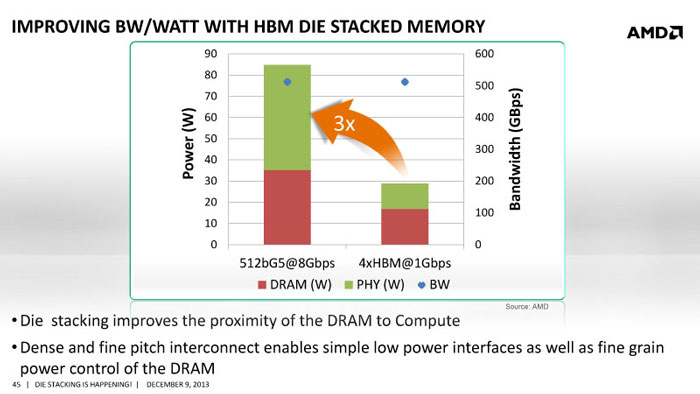

Нетрудно заметить, что по охвату запланированного применения память HBM рассматривается в качестве замены для памяти типа GDDR5. Главное преимущество HBM заключается в том, что эта память использует более простой логический интерфейс, и она располагается максимально близко к CPU или GPU. Как результат, встроенная в HBM логика работает с ощутимо меньшим потреблением, а в целом соотношение пропускной способности на ватт у памяти HBM оказывается в три раза меньше, чем в случае использования памяти типа GDDR5. Как видно на иллюстрации, при организации обмена данными на уровне 512 ГБ/с с использованием микросхем GDDR5 потребление набора составит 80 Вт, тогда как четыре микросхемы (четыре стека) HBM с той же скоростью обмена будут потреблять менее 30 Вт. Разница почти в три раза. И какой разработчик видеокарт не ухватится за такую возможность?

Отметим, что некоторым сдерживающим фактором для широкого распространения HBM DRAM может стать высокая себестоимость решения. Это не только сложность изготовления кристаллов со сквозной металлизацией и последующая упаковка стека с контроллером памяти, но и добавленная стоимость в виде контроллера в составе каждой микросхемы плюс цена базовой соединительной подложки. Поэтому индустрия в качестве возможной альтернативы HBM DRAM в ряде случаев рассматривает модульную компоновку GDDR5 — это ещё один новый стандарт, который носит рабочее название GDDR5M (модуль памяти GDDR5). Память GDDR5M может появиться в 2015 году в составе видеокарт и в качестве оперативной памяти в ноутбуках и настольных системах. Она будет находиться там наряду с памятью DDR4 и HBM DRAM (или HMC). Похоже, разработчикам и производителям скучно не будет.

О подготовке продукции AMD и NVIDIA с использованием памяти HBM DRAM

Ни одна из последних крупных конференций не прошла без демонстрации образцов памяти HBM DRAM компании SK Hynix. Эту память последовательно показывали на конференции ISSCC 2014, на конференции GPU Technology Conference 2014 и на весенней сессии IDF 2014. Массовый выпуск 8-Гбит сборок HBM из четырёх 2-Гбит кристаллов с использованием, предположительно, 29-нм техпроцесса компания SK Hynix начнёт после середины текущего года, и лишь в 2016 году компания перейдёт к производству сборок на основе 8-Гбит кристаллов в стеках до 8 штук. Отметим, всё производство будет лежать в пределах 30-20 нм. Покорять меньшие нормы производства компании остерегаются.

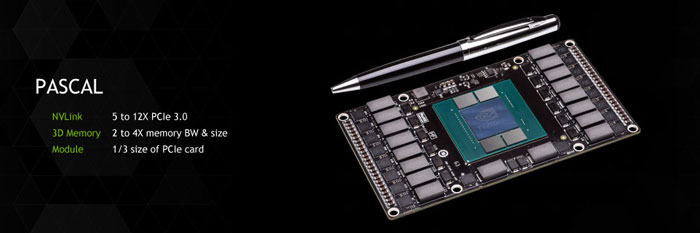

Компания NVIDIA обозначила свою заинтересованность в памяти 3D DRAM (читай — HBM) в момент анонса год назад архитектуры Volta. На нынешней конференции GTC 2014 произошла коррекция данных планов. Теперь мы ожидаем поддержки 3D DRAM со стороны архитектуры NVIDIA Pascal в 2016 году. Поддержка HBM появится, как минимум, в решениях для серверного рынка в виде серверных карт расширения для слота типа «mezzanine»

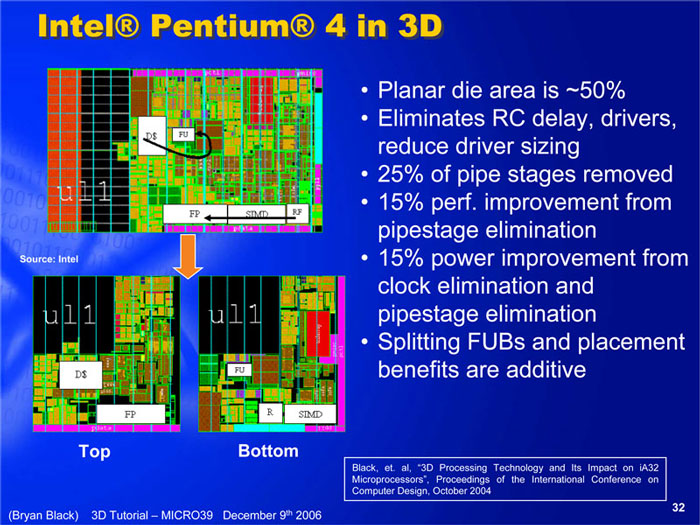

С компанией AMD всё проще. Она не «шифруется» и прямо говорит о будущем использовании памяти HBM и даже подтверждает, что это будут решения компании SK Hynix. Так, председателем профильной рабочей группы JC-42.3 Subcommittee является Джозеф Макри (Joseph Macri), занимающий ныне пост главного технолога группы продуктов AMD (в своё время он работал в компании ATI). Кроме этого в декабре на 46-й ежегодной конференции MICRO 46 одним из ведущих разработчиков компании AMD, Брайаном Блэком (Bryan Black) был зачитан доклад, посвящённый стековым TSVs-соединениям. Пикантность этому докладу добавляет то, что в 2006 году Брайан Блэк, тогда ещё ведущий разработчик компании Intel, на конференции MICRO 39 озвучивал доклад «Design and Fabrication of 3D Microprocessors» и в качестве наглядной иллюстрации использовал стековую конструкцию процессора Pentium 4. Из этого также следует, что компания Intel со временем тоже может перейти к использованию стековой памяти.

Детальнее о структуре памяти HBM DRAM компании SK Hynix

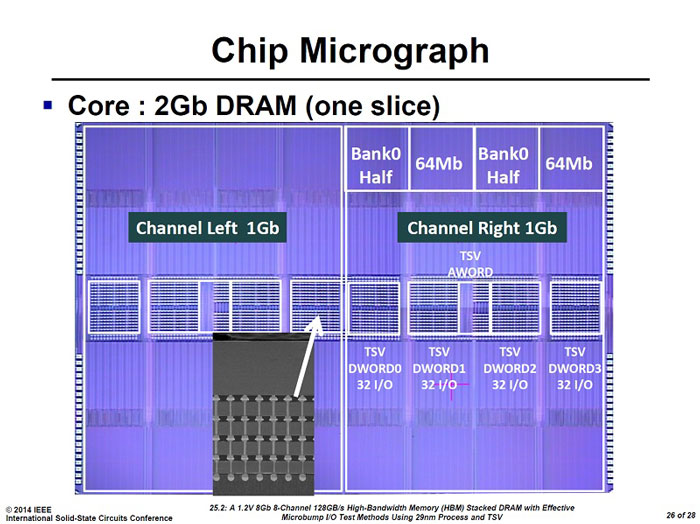

Первое поколение памяти HBM DRAM компании SK Hynix, как мы сказали выше, будет опираться на сборку из четырёх 2-Гбит кристаллов. Строение каждого кристалла (слоя) можно увидеть на картинке ниже.

По центру кристалла расположена зона со сквозными TSVs-соединениями. Всего таких соединений-каналов 1024, хотя контроллер памяти — пятый и нижний слой — будет иметь 1408 контактов. Эти 1408 контактов станут выходом для соединения с CPU или GPU в случае использования общей монтажной подложки (2,5D-упаковка). Блок для обеспечения внешнего сигнального интерфейса должен быть расположен на кристалле контроллера со стороны монтажа процессора. Это обеспечит минимальную длину внешних соединений и поможет избежать появления паразитных ёмкостей.

Контроллер памяти в составе слоя с логикой имеет восемь каналов с разрядностью 128 бит. В перспективе в случае использования восьми кристаллов (слоёв) каждый канал будет обращаться к своему кристаллу. Пока кристаллов в стеке всего четыре, память SK Hynix сконфигурирована таким образом, что к каждому кристаллу имеют доступ два канала, что даёт разрядность 256 бит (минимальная градация при обращении к памяти, таким образом, 32 байта). Каждый из 8 каналов при этом имеет доступ исключительно к своим банкам, которых предусмотрено 8 штук на канал. Каждый из банков, в свою очередь, разбит на два суббанка памяти ёмкостью по 64 Мбит. Другие производители памяти HBM DRAM вольны по-своему конфигурировать кристаллы памяти. Кстати, блоки логики тоже могут иметь различное функциональное наполнение. Компания SK Hynix в составе блока логики стека HBM предусмотрела механизмы для самотестирования ячеек памяти и линий интерфейса с возможность восстанавливать или замещать «битые» ячейки. С учётом того огромного числа контактов и сквозных соединений — это, пожалуй, ключевые механизмы для обеспечения работоспособности памяти HBM DRAM.

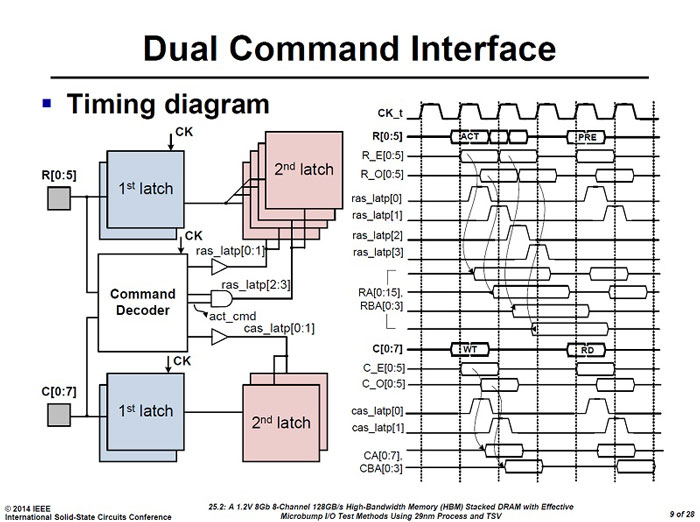

Также отметим наличие двойного командного интерфейса для обращения к банкам памяти HBM DRAM, что даёт возможность одновременного выполнения команд CAS и RAS по адресации к строкам и столбцам, как и возможность организации независимого обновления (refresh) ячеек памяти в своих банках.

В заключение этого небольшого обзора памяти HBM DRAM хотелось бы выразить удивление, что пока в сфере выпуска «широкополосной» памяти себя никак не проявила компания Samsung. Она вместе с компанией Micron являлась организацией консорциума по продвижению памяти HMC, однако за всё прошедшее с тех пор время информации о работе Samsung над микросхемами HMC или HBM не было. Единственное, в чём компания Samsung проявляла активность, так это в выпуске опытных микросхем первого поколения Wide I/O. На этом пока всё.