Ваш город: Москва

Alpha: история в фактах и комментариях

Dig my grave both long and narrow

Make my coffin neat and strong

(из старой американской песни)

Вступление

Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур.

Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит...

Часть 1. PDP и VAX

Digital Equipment Corporation (сокращенно DEC), основанная в 1957 двумя инженерами, Кеннетом Ольсеном (Kenneth Olsen) и Харланом Андерсоном (Harlan Anderson), выпускниками Массачусетского технологического института, была одной из старейших и наиболее значимых компаний мировой компьютерной индустрии.

До основания компании, Ольсен работал в Линкольнской лаборатории при том же институте, содержащейся на средства Министерства обороны США, и участвовал в разработке одного из первых транзисторных компьютеров, TX-2. Первое время компания разрабатывала и продавала элементарные модули для вычислительной техники, но уже в 1960 представила свой первый компьютер, 18-битный PDP-1 (Programmable Data Processor - 1), способный производить около 100 тыс. операций в секунду; кроме всего прочего, именно на нем была написана первая в истории компьютерная игра, Spacewar Стивена Рассела (Steven Russell). 12-битный PDP-8, запущенный в производство в 1964, вполне заслуженно считают первым серийно выпускаемым "миникомпьютером", из-за довольно компактных размеров (с небольшой шкаф) и невысокой, по тем временам, цены (около 18 тыс. долл. США (1965) в базовой комплектации); благодаря отличному соотношению цены и производительности, этот компьютер смог составить достойную конкуренцию знаменитым мэйнфрэймам IBM, и к 1968 было собрано около 1450 машин (не считая поздних многочисленных модификаций). В том же 1968 был представлен 36-битный PDP-10, основанный на дизайне экспериментального PDP-6, рассчитанный на использование в центрах обработки данных, исследовательских лабораториях, и в военных целях; модификации PDP-10 производились вплоть до 1983. Работы над усовершенствованием 36-битной архитектуры продолжались в рамках проекта "Единорог" (the Unicorn project), под руководством Леонарда Хьюджеса (Leonard Hughes) и Дэвида Роджерса (David Rogers), но в июне 1975 проект был закрыт, и все ресурсы были переведены на поддержку другой, 32-битной, архитектуры.

16-битный PDP-11, запущенный в производство в начале 1970-х, был первым компьютером DEC, в котором использовались 8-битные байты, и прямым наследником линейки PDP-8. Благодаря простой и удачной архитектуре, основанной на системной шине Unibus (или её модификации, Q-bus), довольно эффективному набору инструкций, и, что немаловажно, невысокой стоимости, линейка PDP-11 очень быстро обрела популярность. Вполне закономерно, что PDP-11 вскоре стали широко клонировать, в том числе и в "странах народной демократии": СМ-4 (СССР, Болгария, Венгрия), СМ-1420 (СССР, Болгария, ГДР), СМ-1600 (СССР), ИЗОТ-1016 (Болгария), ДВК (СССР). Для PDP-11 было разработано множество операционных систем: DEC предлагала P/OS, RSX-11, RT-11, RSTS/E, также было доступно несколько вариантов DOS, и в конце-концов, на PDP-7 и PDP-11 в 1971 было сделано первое издание ОС UNIX (в Bell Laboratories), тогда ещё на ассемблере. PDP-11 ушел с рынка в течение 1980-х по одной, но неизбежной причине: недостаточный объем адресного пространства, знаменовавший переход на новую, 32-битную, но все ещё CISC, архитектуру.

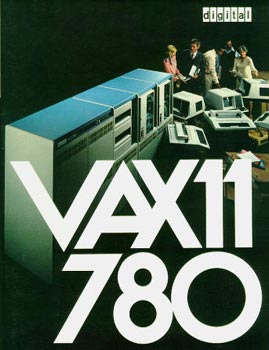

И ей стала VAX (Virtual Address eXtension), официально утвержденная на заседании VAX Architecture Committee в апреле 1975. Детали архитектуры разрабатывались в течение нескольких месяцев в рамках проекта "Звезда" (the Star project) под руководством Гордона Белла (Gordon Bell), параллельно с вышеупомянутым проектом "Единорог", и по окончании работ над обоими проектами было решено отменить дальнейшее развитие 36-битных систем, и сконцентрировать ресурсы на поддержке 32-битных VAX'ов. Фактическим результатом работы проекта "Звезда" было обоснование необходимости как увеличения разрядности основных регистров PDP-11 до 32 бит, так и их числа (с 8 до 16), а также существенный пересмотр набора инструкций. В октябре 1977 был анонсирован первый представитель линейки -- модель 11/780, а в феврале 1978 была выпущена новая операционная система для VAX'ов, VMS (Virtual Memory System) версии 1.0; к слову, новая ОС, многопользовательская и многозадачная, поддерживала до 64Мб оперативной памяти, встроенные сетевые возможности (DECnet), адаптивный планировщик задач, расширенное управление процессами, и многие другие функции, значительно опередившие свое время. В апреле 1980 вышла версия 2.0, с многочисленными улучшениями, переименованная в VAX/VMS. На VAX также была вскоре портирована классическая UNIX. VAX'ы выпускались и продавались с большим успехом в течение 1980-х, и даже на рубеже веков поставлялись ограниченными партиями по спецзаказам. Модельный ряд насчитывал несколько десятков наименований: от довольно компактных рабочих станций до 6-процессорных серверов мэйнфрэйм-класса. И по сей день тысячи VAX'ов работают в структуре Министерства обороны США и NSA (National Security Agency), а также во многих коммерческих организациях. Но тем не менее, эпоха VAX'ов осталась в 1980-х, а в 1990-х DEC сделала ставку на новую архитектуру.

Часть 2. Проект PRISM

В начале 1980-х DEC была на вершине финансового могущества, в значительной мере благодаря стабильно растущим объемам поставок VAX'ов. Однако ничто не вечно, и было очевидно, что в своё время и VAX придется уйти с рынка, как это уже происходило с PDP-11. В то время многие компании начали обращать внимание на перспективные разработки в среде RISC, и DEC явно не желала остаться в стороне. С 1982 по 1985 в составе компании активно работали несколько подразделений, занимавшихся исследованиями в области RISC:

Titan, высокоскоростной дизайн от Западной исследовательской лаборатории (Western Research Laboratory, DECwest) в Пало-Альто (Калифорния), под руководством Фореста Бэскетта (Forest Baskett), с 1982;

SAFE (Streamline Architecture for Fast Execution), под руководством Алана Котока (Alan Kotok) и Дэвида Орбица (David Orbits), с 1983;

HR-32 (Hudson RISC 32-bit), при фабрике DEC в Хадсоне (Массачусетс), под руководством Ричарда Витека (Richard Witek) и Дэниела Добберпуля (Daniel Dobberpuhl), с 1984;

CASCADE Дэвида Катлера (David Cutler) в Сиэттле (Вашингтон), с 1984.

В 1985, с подачи Катлера насчёт создания "корпоративного RISC-плана", все 4 проекта были объединены в один, PRISM (Parallel Instruction Set Machine), и совместными усилиями к августу 1985 была подготовлена первая спецификация на новый RISC-процессор. Стоит упомянуть, что к тому времени DEC уже принималa активное участие в разработке процессора MIPS R3000 и даже инициировалa создание консорциума Advanced Computing Environment для продвижения этой архитектуры на рынке.

Поэтому нет ничего удивительного в том, что разрабатываемый процессор унаследовал много черт, присущих архитектуре MIPS, но в то же время отличия были очевидны. Все инструкции имели фиксированную длину в 32 бита, из них верхние 6 и нижние 5 были собственно кодом инструкции, а остальные 21 предназначались для непосредственно данных либо их адресации. Были определены 64 основных 32-битных целочисленных регистрa (MIPS предусматривалa 32), а также 16 дополнительных 64-битных векторных регистров, и 3 контрольных регистра для векторных операций: два 7-битных (vector length и vector count), один 64-битный (vector mask). Регистр состояния процессора отсутствовал, поэтому результат сравнения двух скалярных операндов помещался в целочисленный регистр, а результат сравнения двух векторных операндов -- в vector mask. Встроенный блок вычислений с плавающей запятой не предусматривался. Также присутствовал набор специальных инструкций (Epicode, или extended processor instruction code), реализованных программно посредством загружаемого микрокода, для облегчения решения специальных задач, присущих определённой среде или операционной системе, и не предусмотренных стандартным набором команд; впоследствии, эта функция была реализована в архитектуре Alpha под названием PALcode (Privileged Architecture Library code).

К 1988 проект был всё ещё в стадии разработки, когда высший менеджмент DEC закрыл его, посчитав дальнейшее финансирование нецелесообразным. Протестуя против этого, Катлер уволился и ушёл в Microsoft, где возглавил подразделение по разработке Windows NT.

В начале 1989 DEC представила свои первые рабочие станции с RISC-процессорами, DECstation 3100 на основе 32-битного MIPS R2000 с частотой в 16МГц, и DECstation 2100 на основе того же процессора, но с частотой в 12МГц. Обе машины работали под ОС Ultrix и стоили довольно умеренно (около 8 тыс. долл. США (1990) за DECstation 2100).

Часть 3. Проект Alpha

В 1989 морально стареющая архитектура VAX уже с трудом могла конкурировать с RISC-архитектурами 2-го поколения, такими как MIPS и SPARC, и было вполне очевидно, что следующее поколение RISC оставит VAX немного шансов на выживание. В середине 1989 перед инженерами DEC была поставлена задача создания конкурентноспособной RISC-архитектуры с перспективным потенциалом, но минимально несовместимой с VAX, чтобы облегчить перенос на неё VAX/VMS и всей сопутствующей программной базы. Также было определено, что новая архитектура должна изначально быть 64-битной, так как конкуренты уже были в процессе перехода на 64 бита. Была создана рабочая группа, в которой главными архитекторами были Ричард Витек и Ричард Сайтс (Richard Sites).

Первое официальное упоминание об архитектуре Alpha датируется 25 февраля 1992, на конференции в Токио. Одновременно в небольшом обзоре (для USENET-конференции comp.arch) были перечислены ключевые моменты новой архитектуры; там же было оговорено, что "Alpha" является кодовым именем нового процессора, а рыночное название будет представлено позже. Процессор имел чистую 64-битную RISC-архитектуру с инструкциями фиксированной длины (по 32 бита), с 32 целочисленными 64-битными регистрами, работал с 43-битными адресами виртуальной памяти (с расширением до 64 бит в перспективе), использовал, как и VAX, little-endian порядок следования байт (то есть, когда младший байт регистра занимает при записи младший адрес в памяти; традиционно поддерживался Intel, в противовес к big-endian, изначально внедрённому Motorola, и используемому в большинстве процессорных архитектур, где младший байт регистра занимает при записи старший адрес в памяти). Математический сопроцессор был изначально интегрирован в ядро, вместе с 32 вещественными 64-битными регистрами, причём использовался произвольный доступ к ним, в отличие от примитивного стекового, используемого сопроцессорами Intel x87. Срок службы новой архитектуры был определен, как минимум, в 25 лет.

Поддерживаемый набор инструкций был максимально упрощён с целью максимального облегчения конвейеризации, и состотоял из 5 групп:

инструкции для целочисленных вычислений;

инструкции для вещественных (с плавающей запятой) вычислений;

инструкции отработки условных и безусловных переходов, а также сравнения;

инструкции загрузки и сохранения данных;

инструкции PALcode.

Стоит отметить, что инструкции целочисленного деления отсутствовали, так как являлись наиболее сложными и плохо поддающимися конвейеризации, а поэтому эмулировались.

Архитектура Alpha была "настоящей" RISC (в отличие от современных процессоров архитектуры i386, которые RISC только изнутри). Концептуально разница между RISC (Reduced Instruction Set Computing) и CISC (Complex Instruction Set Computing) состояла (и до сих пор состоит) в нескольких моментах:

Процессор предполагалось запустить в производство на очень высокой для того времени частоте - 150МГц, и довести до 200МГц при тех же конструкторских нормах. Это оказалось возможным как благодаря удачной архитектуре, так и благодаря отказу разработчиков от использования систем автоматического проектирования и выполнению всех работ по схемотехнике исключительно вручную.

Проект вступил в производственную стадию и вскоре был реорганизован в регулярное подразделение DEC.

Трудами отдела маркетинга DEC новая архитектура получила название AXP (или Alpha AXP), хотя до сих пор неизвестно, аббревиатурой чего было это недоразумение. Возможно, что и ничего; в прошлом DEC имела проблемы с торговой маркой VAX, на которую претендовала компания по производству пылесосов, и тогда дело дошло до суда. Кроме всего прочего мотивировалось, что рекламный слоган этой компании ("Nothing sucks like a Vax!" - "Ничто не сосёт так, как Vax!") дискредитирует продукцию DEC. Так что вскоре в компьютерном мире появилась шутка, что AXP - это "Almost Exactly PRISM", то есть "почти точно PRISM".

Часть 4. EV4, LCA4, EV45, LCA45

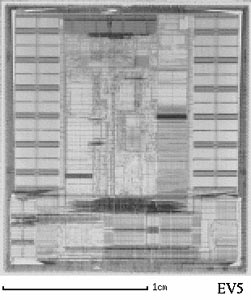

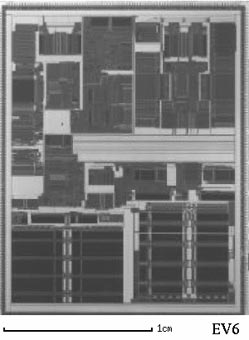

Первый процессор из семейства Alpha получил название 21064 (21 указывал, что Alpha -- это архитектура XXI века, 0 -- процессорное поколение, 64 -- разрядность в битах), и кодовое наименование EV4 (EV является [предположительно] аббревиатурой "Extended VAX", а цифра 4 -- поколением техпроцесса, CMOS4; CMOS, в свою очередь, есть аббревиатура "Complementary Metal Oxide Semiconductor"). Стоит отметить, что прототип EV4 был готов ещё в 1991, по CMOS3 техпроцессу, а поэтому с уменьшенными кэшами и без блока вычислений с плавающей запятой; тем не менее, он сыграл свою роль в отладке архитектуры и программной среды. EV4 был представлен в ноябре 1992, и поступил в производство на передовом для того времени 3-слойном 0,75µ техпроцессе (впоследствии, производство было переведено на оптическую модификацию CMOS4 -- CMOS4S, 0,675µ). Был рассчитан на напряжение питания в 3,3В, выпускался с тактовыми частотами от 150МГц до 200МГц (ТDP от 21Вт до 27Вт). Состоял из 1,68 млн. транзисторов, и имел площадь ядра в 233 кв.мм. Поддерживал многопроцессорность, как один из ключевых моментов архитектуры. Форм-фактор: PGA-431 (Pin Grid Array).

Кэш L1 был интегрирован: 8Кб для инструкций (I-cache, instruction cache), с прямым отображением (direct-mapped), а также 8Кб для данных (D-cache, data cache), с прямым отображением и сквозной записью (write-through). Задержки при чтении из D-cache составляли 3 такта. Каждая линия I-cache состояла из 32 байт инструкций, 21-битного тега, 8-битного поля истории переходов, и нескольких вспомогательных полей; каждая линия D-cache состояла из 32 байт данных и 21-битного тега. Кэш L2 (B-cache, backup cache) был рекомендуемой опцией, набирался на микросхемах синхронной или асинхронной статической памяти, работал в режиме обратной записи (write-back) с прямым отображением и упреждающим чтением (read-ahead), мог иметь размер до 16Мб (обычно от 512Кб до 2Мб); каждая линия состояла из 32 байт данных или инструкций с 1-битным long-word parity или 7-битным long-word ECC, максимум 17-битного тега с 1 битом чётности, и 3 битов состояния с 1 битом четности. Скорость чтения/записи B-cache программировалась, в тактах процессора. Разрядность системной шины данных составляла 64 или 128 бит (программируемо, с 1-битным long-word parity или 7-битным long-word ECC), и она мультиплексировалась с шиной данных B-cache, переключаясь при необходимости; разрядность системной шины адреса составляла 34 бита. Организационно B-cache был включающим (inclusive) D-cache, то есть поддерживал копию содержимого последнего. При выгрузке данных из B-cache в память использовался механизм victim write. Операции чтения/записи в B-cache являлись прерогативой исключительно процессора, для системной логики было разрешено только чтение файла тегов (B-tag, что жизненно необходимо особенно в многопроцессорных системах, для обеспечения согласованности (когерентности) кэшей).

Процессор имел один целочисленный конвейер (E-box, 7 стадий), и один вещественный конвейер (F-box, 10 стадий). Декодер и планировщик инструкций (I-box) был в состоянии подавать 2 команды за такт в порядке очереди (in-order) на исполняющие устройства, то есть на E-box, F-box и блок загрузки/сохранения (A-box). Контроллер кэшей и системной шины (C-box) работал в тесном взаимодействии с A-box и управлял как интегрированными I-cache и D-cache, так и внешним B-cache. Также присутствовал блок предсказания переходов (branch prediction unit), с таблицей переходов на 4096 записей (branch history table), по 2 бита каждая. I-TLB имел 8 записей для 8Кб-страниц, и 4 записи для 4Мб-страниц, все с пoлной ассоциативностью (fully-associative). D-TLB имел 32 записи, с полной ассоциативностью.

Несмотря на отличную производительность, EV4 был довольно дорог для значительной части потенциальных покупателей, и поэтому в сентябре 1993 был анонсирован его бюджетный собрат, 21066 (LCA4, или LCA4S). Этот процессор был основан на ядре 21064, но с дополнительно интегрированными контроллерами памяти и шины PCI, а также некоторыми второстепенными функциями. Однако, разрядность системной шины данных была урезана до 64 бит, что негативно сказалось на производительности. LCA4 производился по 0,675µ CMOS4S техпроцессу, и его площадь оказалась ещё меньше, чем у EV4 (209 кв.мм по сравнению с 234 кв.мм.), а тактовые частоты были занижены (от 100МГц до 166МГц), в значительной мере из-за потенциальной угрозы перегрева в плохо вентилируемых настольных системных блоках того времени, и чтобы не создавать дополнительной конкуренции EV4. Количество транзисторов в ядре составило 1,75 млн., a напряжение питания -- 3,3В. Дизайн этого процессора был лицензирован Mitsubishi, и последняя также производила LCA4 (включая и 200МГц версию).

В октябре 1993, на Microprocessor Forum, был анонсирован 21064А (EV45), обновленная версия EV4, производимая по 4-слойному 0,5µ CMOS5 техпроцессу. В ноябре 1994, на COMDEX'94, был представлен 21066А (LCA45), почти аналогично модифицированная версия LCA4. Стоит отметить, что манера маркетологов DEC добавлять букву к модели процессора при перепланировке ядра под новый техпроцесс сохранилась и в будущем. Собственно состав процессорных ядер изменился незначительно; EV45 теперь обладал удвоенным размером кэша L1 (16Кб I-cache + 16Кб D-cache), к полям данных и тегам I-cache и D-cache было добавлено по биту чётности, поля истории переходов I-cache были расширены до 16 бит, ассоциативность D-cache была увеличена до 2 (2-way set associative), а к режимам контроля над системной шиной данных был добавлен 1-битный byte parity. Также в EV45 и LCA45 был незначительно модифицирован F-box (оптимизация деления: в EV4 одна операция требовала 34 такта для операндов одинарной точности и 63 такта для операндов двойной точности, вне зависимости от значений операндов; в EV45 она уже требовала от 19 до 34 тактов для операндов одинарной точности и от 29 до 63 тактов для операндов двойной точности, в зависимости от значений операндов). LCA45 также производился на мощностях Mitsubishi. Площади ядер уменьшились: до 164 кв.мм (EV45) и до 161 кв.мм (LCA45), количество транзисторов в ядре EV45 возросло до 2,85 млн., а в ядре LCA45 осталось прежним (1,75 млн.). В конечном результате, энергопотребление обоих процессоров в расчёте на единицу частоты сократилось, хотя напряжение питания осталось неизменным (3,3В). Тактовые частоты ЕV45 составляли от 200МГц до 300МГц (TDP от 24Вт до 36Вт), LCA45 -- от 166 до 233МГц.

Так как DEC участвовала в разработках оборудования под заказ Министерства обороны США, то в 1994 были спроектированы процессоры 21068 (66МГц) и 21068А (100МГц), являвшиеся вариантами LCA4 и LCA45, адаптированными под военные нужды (пассивное охлаждение, жёсткие температурные условия, пр.).

Первые чипсеты для EV4 использовали периферийные шины TURBOchannel, FutureBus+ и XMI. Хотя все эти реализации были очень скоростными для своего времени (около 100Мб/с на шину), они не получили широкого распространения, и количество доступной периферии измерялось единицами. Поэтому DEC обратила внимание на стандартные шинные архитектуры, такие как PCI и ISA (EISA). В начале 1994 был представлен чипсет DEC Apecs в двух исполнениях: с 64-битной системной шиной данных (21071) и 128-битной (21072). Вся разница между ними состояла в том, что 21071 состоял из 4 миросхем (1 универсальный контроллер, 2 микросхемы data slice, 1 контроллер шины PCI), а 21072 -- из 6 (дополнительно ещё 2 микросхемы data slice). Поддерживал частоту системной шины в 33МГц, до 16Мб B-cache и до 4Гб памяти FPM parity со временем доступа от 100 до 50нс. Поддержка шин ISA или EISA могла быть реализована посредством стандартных мостов, таких как i82378IB (ISA) или i82378EB (EISA).

Первая рабочая станция архитектуры Alpha от DEC была выпущена в ноябре 1992, DEC 3000 Model 500 AXP (кодовое имя Flamingo), с процессором EV4 150МГц, 512Кб B-cache, 32Мб оперативной памяти, SCSI HDD на 1Гб, SCSI CD-ROM, встроенным контроллером Ethernet 10Мбит (толстый коаксиал и витая пара), встроенным звуковым и ISDN контроллером, а также с 19-дюймовым монитором (1280х1024 8-бит). Цена была шокирующая: 38995 долл. США.

Часть 5. EV5, EV56, PCA56, PCA57

Первая архитектурная информация о своём Alpha-процессоре 2-го поколения была открыта DEC на конференции Hot Chips, которая состоялась 14 августа 1994 в Пало-Альто (Калифорния), хотя официальным анонсом 21164 (EV5) можно считать пресс-релиз DEC от 7 сентября 1994. Процессор базировался на ядре EV45 и содержал изменения скорее экстенсивного характера, чем интенсивного. Ядро включало удвоенное количество конвейеров для целочисленной и вещественной математики (по сравнению с EV4 или EV45), причём количество стадий вещественных конвейеров сократилось с 10 до 9. Однако, целочисленные конвейеры были неодинаковы: хотя оба могли выполнять элементарные арифметические и логические операции, только в компетенцию 1-го входило выполнение инструкций умножения и смещения, и только по 2-му могли быть направлены инструкции условных/безусловных переходов; также, оба конвейера могли вычислять виртуальные адреса для команд загрузки, однако только 1-й -- для команд сохранения. Вещественные конвейеры были также неоднородны: 1-й мог выполнять любой код с плавающей запятой, кроме инструкций умножения, которые были теми единственными командами, что мог выполнять 2-й конвейер. Чтобы обеспечить эффективную загрузку функциональных устройств, I-box мог выбирать и декодировать до 4 инструкций за такт. Производился по тому же 4-слойному 0,5µ CMOS5 техпроцессу, что и EV45, был рассчитан на напряжение питания в 3,3В, имел площадь ядра в 299 кв.мм. и содержал 9,3 млн. транзисторов (из них 7,8 млн. в виде интегрированного кэша), что было очень близко к теоретическому пределу для данного техпроцесса. Тактовые частоты EV5 составляли от 266МГц до 333МГц (TDP от 46Вт до 56Вт). Форм-фактор: IPGA-499 (Interstitial Pin Grid Array).

Размеры и организация I-cache и D-cache остались как у EV4, то есть по 8Кб, и со сквозной записью для D-cache, хотя он теперь стал двухпортовым по чтению, то есть за 1 такт он мог поставить данные для 2 инструкций загрузки. Жертвуя транзисторами во имя быстродействия, физически D-cache состоял из 2 абсолютно одинаковых по содержанию частей размером в 8Кб каждая, то есть чтение шло из любой части, а запись -- одновременно в обе. Так как процессор имел 96Кб интегрированного кэша L2 с обратной записью с 3-канальной ассоциативностью, то в структуру C-box была добавлена его поддержка (S-cache, secondary cache) через независимую 128-битную шину данных, при этом интерфейс к внешнему B-cache (который все ещё оставался опциональным, набирался на микросхемах синхронной статической памяти и мог иметь размер до 64Мб, хотя обычно составлял от 1Мб до 4Мб) был сохранён -- другими словами, EV5 поддерживал 3 уровня кэшей. Доступ к S-cache был организован по принципу 4-стадийного конвейера: два такта на поиск тега и его изменение, два такта на доступ к данным и их передачу; строка S-cache была в 64 байта (с возможным разделением на две 32-байтных подстроки), с одним тегом на строку. Задержки при чтении из D-cache сократились до 2 тактов, а из S-cache -- составляли 7 тактов (как упоминалось выше, 4 такта на первые 16 байт, и по 1 такту на каждые последующие 16 байт для формирования полной строки). Как и в EV4, содержимое D-cache дублировалось, только теперь в S-cache; в свою очередь, для упрощения поддержки, B-cache был включающим S-cache, несмотря на разницу в ассоциативностях. Ёмкость I-TLB была увеличена до 48 записей (страницы размером от 8Кб до 4Мб), а D-TLB -- до 64 записей, причём он стал двухпортовым (по аналогии с D-cache). Системная шина данных имела фиксированную ширину в 128 бит (с дополнительными 16 битами для ECC) и всё так же мультиплексировалась с шиной данных к B-cache; системная шина адреса была 40-битной, управления -- 10-битной.

В октябре 1995, на Microprocessor Forum, был представлен 21164А (EV56), незначительно модифицированная версия EV5 с учетом 0,35µ конструкторских норм (CMOS6), производимая на той же фабрике в Хадсоне (DEC инвестировала в её модернизацию около 450 млн. долл США). Наиболее существенным архитектурным отличием можно считать BWX (Byte-Word Extension) -- набор из 6 дополнительных команд для загрузки/сохранения данных размером в 8 или 16 бит. Изначально архитектура Alpha поддерживала загрузку/сохранение данных квантами исключительно по 32 или 64 бита, что создавало определенные сложности при портировании или эмуляции кода других процессорных архитектур, например, i386 или MIPS. Предложение о внедрении BWX в базовый набор команд Alpha появилось в июне 1994 с подачи Ричарда Сайтса и было утверждено в июне 1995. Правда, для успешной работы BWX требовалась поддержка как со стороны процессора, так и со стороны чипсета. EV56 производился с тактовыми частотами от 366МГц до 666МГц (TDP от 31Вт до 55Вт), начиная с лета 1996. Samsung также выпускал EV56, по лицензионному соглашению с DEC от июня 1996 (версию на 666МГц производил только он). Содержал 9,66 млн. транзисторов, площадь ядра составляла 209 кв.мм., использовалось двойное напряжение (2,5В на основную логику и 3,3В на входные-выходные цепи).

17 марта 1997 был представлен 21164PC (PCA56), бюджетный вариант EV56, спроектированный совместно DEC и Mitsubishi. Отсутствовал S-cache и соответствующая логика, зато размер I-cache был увеличен вдвое (до 16Кб). Содержал 3,5 млн. транзисторов, имел площадь ядра в 141 кв.мм., использовал тот же техпроцесс и напряжение питания, что и EV56; форм-фактор процессора изменился: IPGA-413 против IPGA-499. Выпускался с тактовыми частотами от 400МГц до 533МГц (TDP от 26Вт до 35Вт). В будущем, на производственных мощностях Samsung, также выпускался 0,28µ вариант 21164PC (PCA57), с удвоенными размерами I-cache и D-cache, причём первый использовал 2-канальную ассоциативность. Количество транзисторов в ядре увеличилось до 5,7 млн., а его площадь уменьшилась (до 101 кв.мм.); был спроектирован под пониженное напряжение питания (2,0В на основную логику и 2,5В на входные-выходные цепи), с тактовыми частотами от 533МГц до 666МГц (TDP от 18Вт до 23Вт).

Кроме унаследованных от EV56 инструкций BWX, PCA56 поддерживал новый набор MVI (Motion Video Instructions), предназначенный для ускорения алгоритмов обработки видео и аудио потоков по принципу SIMD (Single Instruction -- Multiple Data), в некоторой мере сопоставимый с MMX.

Первым стандартным чипсетом, разработанным для EV5, был DEC Alcor (21171). Он поддерживал частоту системной шины в 33МГц, до 64Мб B-cache, до 8Гб памяти FPM ECC (используя шину памяти разрядностью в 256 бит), а также 64-битную шину PCI (33МГц). Поддержка шины ISA (EISA) могла быть реализована посредством стандартного моста, как и прежде. Встроенного контроллера IDE также не было (мог устанавливаться отдельной микросхемой других производителей). Физически чипсет состоял из 5 чипов: 1 универсального контроллера (включающего поддержку шины PCI), и 4 коммутаторов данных (data switch). Одновременно с запуском в производство EV56 была выпущена модификация Alcor, поддерживающая BWX -- Alcor 2 (21172). Дальнейшим развитием этой "чипсетной династии" стал одночиповый Pyxis (21174), который поддерживал системную шину с частотой в 66МГц и память SDRAM ECC 66МГц (правда, используя шину памяти с разрядностью в 128 бит). Для систем на основе PCA57 был разработан чипсет VLSI Polaris.

Часть 6. Крах DEC

26 января 1998 компьютерный мир обошла новость, что находящаяся в критическом финансовом положении DEC была куплена Compaq, и что сделка находится в процессе утверждения собраниями акционеров обеих компаний. Акционеры DEC ратифицировали соглашение 2 февраля 1998. Сумма сделки составила 9,6 млрд. долл. США, при ориентировочной рыночной капитализации DEC приблизительно в 7 млрд. долл. США. Начавшийся вскоре процесс интеграции подразделений DEC в структуры Compaq привёл к тому, что уже через полгода DEC окончательно прекратила своё существование (11 июня 1998 её акции перестали котироваться на Нью-Йоркской фондовой бирже). Стоит отметить, что переговоры между DEC и Compaq велись ещё с 1995, но сорвались в 1996 из-за позиции менеджента DEC, настаивавшего на именно слиянии компаний, а не поглощении. Тем не менее, вполне закономерен вопрос: как могло так случиться, что огромная компания (по состоянию на 1989: почти 130 тыс. человек персонала, общий объём продаж около 14 млрд. долл. в год, то есть второй показатель по отрасли после IBM), с очень высоким исследовательским потенциалом и значительной производственной базой, была вынуждена продать себя крупному сборщику компьютерной техники из Техаса? Однозначного ответа на этот вопрос никто так и не дал, хотя причины называли разные. Об этом, и подробнее.

Давным-давно Кеннет Ольсен, основатель, президент и главный исполнительный менеджер DEC почти до самого её конца, сказал, что хорошие с инженерной точки зрения продукты продают себя сами. А следовательно в рекламе или ином продвижении не нуждаются. Ему также принадлежит изречение, что нет причины, из-за которой каждый захотел бы иметь компьютер у себя дома. Возможно, эти мысли оправдывали себя в "добрые старые" времена, когда компьютерная техника производилась в небольших количествах профессионалами для профессионалов и стоила довольно больших денег, но не в конце 20-го века, когда её продавали миллионами штук в год, и когда самый обыкновенный компьютер можно было собрать максимум за час времени при помощи отвёртки и деталей из ближайшего компьютерного магазина, и за сумму на порядок меньшую предыдущей. В конце концов, купить его целиком в том же магазине, ещё и с доставкой на дом. А если учесть, что покупать такой компьютер будет не менеджер с техническим образованием, прекрасно осознающий глубину смысла термина TCO (Total Cost of Ownership, совокупная стоимость владения), а некая тётя Маша или представитель подрастающего поколения Вовочка, в принципе не отличающие транзистор от резистора, то таких покупателей надо мотивировать явно не инженерными достоинствами потенциального приобретения. Ошибка #1.

Ещё в самом начале развития архитектуры Alpha высшим руководством DEC был допущен большой стратегический просчёт. Как известно, прототипы EV4 были продемонстрированы DEC на компьютерной конференции в феврале 1991. Среди присутствующих были инженеры Apple Computer, которые в то время занимались поиском новой процессорной архитектуры для будущих компьютеров компании, и возможности EV4 произвели на них впечатление. В июне того же года Джон Скалли (John Sculley), в то время главный исполнительный менеджер Apple, встретился с Кеннетом Ольсеном, и предложил использовать новый процессор DEC в будущих Маках. Ольсен отклонил предложение Скалли, мотивируя тем, что процессор ещё не готов для рынка, а архитектура VAX ещё не исчерпала себя. Через несколько месяцев было объявлено, что новые Маки будут использовать процессоры PowerPC от альянса Apple, IBM и Motorola. Позже Вильям Деммер (William Demmer), бывший вице-президент подразделений VAX и Alpha, ушедший в отставку в 1995, заявил в интервью Business Week от 28 апреля 1997: "Кен не хотел, чтобы будущее компании зависело от Alpha." Ошибка #2.

DEC сама производила как процессоры Alpha, так и чипсеты для них на своей фабрике в Хадсоне (Массачусетс), а также многочисленную периферию. Она также сама разрабатывала и изготовляла материнские платы, хотя и в довольно ограниченном ассортименте, и исключительно "десктопной" направленности (эти платы так и назывались, Evaluation Board или AlphaPC). Несмотря на то, что почти все без исключения Alpha-сервера DEC были многопроцессорными, ни одна из этих материнских плат SMP не поддерживала. Тем не менее, все материнские платы были выполнены на высоком техническом уровне, хотя и стоили недёшево, как и процессоры Alpha. Схемотехника этих плат была в свободном доступе, поэтому некоторые компании (Aspen, Polywell, Enorex, др.) производили их клоны; единственной компанией, разработавшей и прооизводившей свои платы, была DeskStation. В целом, можно смело утверждать, что приоритетом для DEC была продажа собственных рабочих станций и серверов, а не рынок комплектующих для тех же рабочих станций и серверов. С таким походом к делу можно как-то выжить, но нельзя победить в борьбе за рынок. Ошибка #3.

Несмотря на все попытки, DEC так и не смогла сделать цены на свою продукцию (акцентируя внимание на процессорах, чипсетах и материнских платах) доступными широким слоям потенциальных покупателей. Например, 266МГц и 300МГц EV5 по состоянию на начало 1995 стоили соответственно 2052 и 2937 долл. США в партиях по 1000 шт. -- непомерные цены, даже учитывая среднюю стоимость производства (модель MPR) в 430 долл. США за шт. В расчёте на один "попугай" SPECint92, EV5 стоил приблизительно в 2 раза дороже RISC-процессоров других производителей! При этом стандартный чипсет к нему, Alcor, продавался не в пример дешевле -- 295 долл. США в партиях по 5000 шт., хотя материнская плата на его основе (EB164, с 1Мб B-cache), вместе с процессором и 16Мб оперативной памяти (чего, кстати, было явно недостаточно для большинства задач, даже по меркам того времени), предлагалась по цене около 7500 долл. США. Ошибка #4.

Хотя Alpha была изначально объявлена "открытой архитектурой", консорциум по её развитию так и не был создан. Разработки велись усилиями DEC, иногда сообща с Mitsubishi. Получалось, что хотя собственно архитектура и была свободной де-юре, её основные разработки являлись очень даже закрытыми де-факто, так как патентовались соответствующим образом и подлежали платному лицензированию (если вообще подлежали), что мало способствовало успешному продвижению на рынке. Стоит отметить, что вскоре после выпуска EV4 руководство DEC предлагало лицензировать производство процессора Intel, Motorola, NEC, и Texas Instruments. Но эти компании имели свои разработки и были малозаинтересованы или незаинтересованы совсем в EV4, а потому отказались. Не исключено, что условия могли быть непреемлемы, или что-нибудь ещё. Ошибка #5.

Далее, даже самый быстрый компьютер без операционной системы и нужного программного обеспечения -- всего лишь дорогой источник шума и обогреватель окружающей среды. Свою Alpha-продукцию DEC позиционировала для Windows NT, Digital UNIX, и OpenVMS, причем именно в таком порядке приоритетности. Оно бы и ничего, но...

Windows NT -- это операционная система, изначально рассчитанная на пользователя, а не на программиста (так как не содержала никаких встроенных средств для разработки ПО), и поэтому сильно зависела от откомпилированного для неё ПО, и в первую очередь, коммерческого. А если смотреть фактам в лицо, то количество приложений, доступных для Alpha, отличалось в разы от аналогичного показателя для i386. Ситуацию в некоторой мере мог исправить FX!32, выпущенный в 1996 командой Антона Чернова (Anton Chernoff), отличный эмулятор и транслятор кода x86 в код Alpha, но от падения производительности как минимум на 40% не спасал, по сравнению с изначально откомпилированными под Alpha приложениями. Далее, драйвера как категория ПО; тут FX!32 ничем помочь не мог, и дела обстояли ещё хуже -- очень немногие производители сочли выпуск версий для Alpha целесообразным, поэтому приходилось рассчитывать, в основном, на Microsoft и DEC. В конце-концов, Windows NT (как 3.51, так и 4.0) была 32-битной ОС, даже работая на 64-битной архитектуре Alpha, и поэтому не могла полностью раскрыть потенциал последней. Тем не менее, все эти оказии не мешали DEC продвигать свои Alpha-системы под слоганом "Рождён для работы с Windows NT" ("Born to run Windows NT"). В общем, такая ОС не должна была позиционироваться как основная для архитектуры Alpha, хотя собственно факт возможности её установки был большим плюсом для архитектуры. Ошибка #6.

OpenVMS и Digital UNIX (также известная как DEC OSF/1, и позднее как Compaq Tru64 UNIX), две надёжные и масштабируемые коммерческие операционные системы от DEC, так и не обрели широкой популярности из-за высоких цен (например, свыше 1000 долл. США за одну копию Digital UNIX 4.x в 1997), и, как следствие, закрытости исходного кода. Хотя с этими ОС были связаны и другие сложности (например, поддержка аппаратной базы была ещё более ограниченной, чем у Windows NT), но eсли хотя бы одна из этих ОС получила свободу, вместе с теми отличными инструментами для разработки ПО от DEC, то это могло серьёзно укрепить рыночные позиции архитектуры Alpha. Ошибка #7.

DEC никак не поддерживала бесплатные операционные системы с открытым кодом, хотя первая из них (NetBSD) была портирована на Alpha в 1995, а вслед за ней Linux, OpenBSD и FreeBSD. Это было, как минимум, странно, потому что и по сей день в этом сегменте архитектура Alpha пользуется широкой популярностью, и рыночная ценность вышеупомянутых ОС была очевидна даже на то время, постоянно увеличиваясь. Кроме того, эти ОС обеспечивали не худшее быстродействие по сравнению с коммерческими Digital UNIX и OpenVMS, и сопоставимую с Windows NT поддержку аппаратной части (намного лучшую с точки зрения дня сегодняшнего), и многие другие преимущества, которые можно ожидать от ПО с открытым кодом. Oшибка #8.

В список ошибок DEC можно было ещё включить игнорирование революции массовых и недорогих персональных компьютеров, чрезмерную диверсификацию бизнеса, и прочие менее значительные, но так как они не связаны непосредственно с архитектурой Alpha, можно подвести итоги. С точки зрения автора, DEC приложила множество усилий, чтобы заработать как можно больше денег при помощи архитектуры Alpha, но не приложила почти никаких усилий, чтобы помочь собственно архитектуре.

Из-за многочисленных неудач DEC в конце 1980-х и начале 1990-х, решением совета директоров в июле 1992 Ольсен был отстранён от руководства компанией, и на его место пришёл Роберт Палмер (Robert Palmer). В 1994 по его инициативе была проведена полная реорганизация менеджмента компании, которая из "матричной" (когда функционально разные отделы компании тесно взаимодействовали между собой при принятии решений) трансформировалась в традиционную "вертикальную" (с чётко выраженными полномочиями и обязанностями от самого верха компании и до самого низа). Чистые убытки DEC за период с 1991 по 1994 составили свыше 4 млрд. долл. США, из них 2 млрд. только с июля 1993 по июль 1994 (учитывая 1,2 млрд. на реорганизацию), а количество персонала сократилось до 85 тыс. чел. Согласно программе Палмера, следовало избавиться от подразделений, не являющихся приоритетными для компании, и с этого момента началась глобальная распродажа. В июле 1994 за 400 млн. долл. США было продано Quantum подразделение по разработке и производству дисковых и ленточных накопителей (Storage Business Unit), вскоре после провала первых моделей жёстких дисков с тонкоплёночным покрытием пластин (RA90 и RA92), слишком поздно вышедших на рынок из-за недоработок при проектировке, и не выдержавших конкуренции. В августе 1994 за 100 млн. долл. США было продано Oracle подразделение баз данных (Database Software Unit), и тогда же за 140 млн. долл. США была продана 7,8% доля в итальянской Olivetti. В ноябре 1997 была подписана сделка о продаже Cabletron за 430 млн. долл. США подразделения сетевых решений (Network Product Business Unit).

Kонец DEC был довольно громким. В мае 1997 она подала в суд на Intel, обвиняя последнюю в нарушении 10 своих патентов на архитектуру Alpha при проектировании процессоров Pentium, Pentium Pro и Pentium II. В сентябре 1997 Intel ответила встречным иском, обвиняя DEC в нарушении 14 патентов при разработке процессоров Alpha. В конце-концов, 27 октября 1997 мир был подписан: обе компании отзывают свои претензии, DEC предоставляет Intel производственные права на весь спектр своей продукции (кроме сегмента Alpha), и соглашается поддерживать будущую архитектуру IA-64, а Intel выкупает у неё за 625 млн. долл. США фабрику в Хадсоне вместе с проектными центрами в Иерусалиме (Израиль) и Остине (Техас), и берётся за производство процессоров Alpha в будущем. Кроме того, был подписан договор о взаимном кросс-лицензировании патентов сроком на 10 лет. Сделка была завершена 18 мая 1998; к тому времени Compaq уже адаптировала в свои структуры основные подразделения DEC, включая 38 тыс. сотрудников (по сравнению с 32 тыс. у самой Compaq до поглощения), хотя значительная их часть всё же была сокращена в самом ближайшем будущем.

Стоит упомянуть, что незадолго до конца DEC, а также вскоре после этого, многие ведущие инженеры, которым DEC была обязана своим могуществом, ушли к другим работодателям: Деррик Мейер (Derrick Meyer) ушёл в AMD создавать K7; туда же, но архитектором K8, ушел Джеймс Келлер (James Keller); Дэниел Лейбхольц (Daniel Leibholz) ушёл в Sun разрабатывать UltraSPARC V; также уволился Ричард Сайтс, один из ведущих разработчиков архитектуры Alpha на протяжении всего времени её существования. В этом плане Intel повезло ещё меньше: доставшаяся ей от DEC архитектура StrongARM осталась почти без разработчиков, так как никто из ведущих инженеров, проектировавших StrongARM-110, а именно Дэниел Добберпуль, Ричард Витек, Грегори Хеппнер (Gregory Hoeppner) и Лайэм Мэдден (Liam Madden), не пожелал перейти на работу в Intel, а команда разработчиков StrongARM второго поколения, работавшая под руководством Витека в Остине, уволилась в полном составе, так что Intel пришлось разрабатывать ядро в буквальном смысле с нуля, усилиями своих инженеров, до этого разрабатывавших i960.

Часть 7. EV6, EV67, EV68C, EV68A

Хотя процессор 21264 (EV6) был разработан в DEC, и первая информация о нем была опубликована в октябре 1996 на Microprocessor Forum, окончательное воплощение в кремнии датируется февралём 1998, когда DEC уже была в процессе ликвидации. Собственно процессор представлял собой довольно существенный шаг вперед по сравнению с EV5, во многих аспектах революционный. Одним из основных нововведений было внеочередное исполнение (out-of-order execution) инструкций, повлёкшее за собой фундаментальную реорганизацию ядра, и снизившую зависимость основных фунциональных устройств от пропускной способности кэшей и оперативной памяти. EV6 мог переупорядочить на лету до 80 инструкций, а это значительно больше, чем у других конкурентных разработок (к слову, архитектура Intel P6 предусматривала внеочередную обработку до 40 [микрокоманд], HP PA-8x00 -- до 56, MIPS R12000 -- до 48, IBM Power3 -- до 32, а PowerPC G4 -- до 5; разработанный к тому времени Sun UltraSPARC II переупорядочивание команд не поддерживал). Внеочередное исполнение дополнялось техникой переименования регистров (register renaming), и для этого в ядро было встроено дополнительно 48 целочисленных и 40 вещественных физических регистров (количество логических, то есть программных, осталось неизменным).

Количество целочисленных конвейеров было увеличено до 4 (организованных в 2 кластера), но функционально они были несколько неоднородны: 2-й конвейер мог выполнять операции умножения (7 тактов на инструкцию) и сдвига (1 такт), а 4-й -- MVI (3 такта) и сдвига; кроме того, все 4 конвейера поддерживали отработку элементарных арифметических и логических операций (1 такт). Каждый кластер располагал своим файлом целочисленных регистров (как упомянуто выше, на 80 записей), содержимое которых было идентично (синхронизировалось). 1-й и 3-й конвейеры также выполняли некоторые функции A-box, рассчитывая виртуальные адреса для операций загрузки/сохранения. Собственно A-box работал с I-TLB и D-TLB (каждый на 128 записей), очередями загрузки и сохранения (каждая по 32 команды), и 8 64-байтными буферами (miss address file) для операций с B-cache и основной памятью. Вещественные конвейеры также были функционально различны: 1-й поддерживал операции сложения (4 такта), деления (12 тактов для одинарной точности и 15 тактов для двойной), вычисления квадратного корня (15 и 30 тактов), а 2-й -- только умножения (4 такта). Между прочим, блок вычисления квадратного корня и соответствующие инструкции были нововведениями для архитектуры Alpha. Декодер, как и прежде в EV5, подавал до 4 инструкций за такт, а планировщик распределял их в 2 очереди: на целочисленные конвейеры (I-queue, 20 команд), и на вещественные конвейеры (F-queue, 15 команд). Кроме вычисления квадратного корня, были добавлены инструкции предварительной выборки, а также команды для переноса данных между целочисленными и вещественными регистрами.

Структура C-box подверглась значительным изменениям: теперь он работал только с 2 уровнями кэш-памяти. Интегрированный в ядро L1 состоял из 64Кб I-cache и 64Кб D-cache, оба с 2-канальной ассоциативностью и 64-байтными строками, причем D-cache работал в режиме обратной записи, хотя всё так же дублировался в B-cache. Из-за значительных размеров и усложнённой организации задержки D-cache при чтении/записи были увеличены до 3 тактов (в/из целочисленного регистра) и 4 тактов (в/из вещественного регистра). D-cache так и остался двухпортовым, но, в отличие от EV5, он уже не состоял из 2 одинаковых частей, синхронизированных по записи, а был просто заведён на удвоенной частоте. Внешний B-cache, размером от 1Мб до 16Мб с прямым отображением и обратной записью, использовал независимую 128-битную двунаправленную шину данных (с дополнительными 16 битами для ECC), а также независимую 20-битную однонаправленную шину шину адреса; набирался на микросхемах LW SSRAM (late-write, с отложенной записью), а позднее и DDR SSRAM (double data rate, с удвоенной скоростью передачи данных); частота B-cache программировалась (от 2/3 до 1/8 частоты ядра), и, в отличие от предыдущих поколений процессоров Alpha, собственно B-cache не был опциональным. Системная шина данных была только 64-битной (с дополнительными 8 битами для ECC), двунаправленной, но использовала технологию DDR. Системная шина адреса была 44-битной, физически представленная в виде двух 15-битных однонаправленных каналов, без поддержки DDR. 15-битная системная шина управления DDR также не поддерживала. Был изменён базовый принцип работы системной шины, которая теперь стала выделенной (вместо разделяемой), то есть каждый процессор имел свой путь к чипсету.

Блок предсказания ветвлений был полностью переработан. Теперь он был организован по 2-уровневой схеме: с локальной историей переходов (local history table, 1024 записи с 10-битными счетчиками) и локальным предсказателем (local predictor, 1024 записи по 3 бита), а также с глобальным предсказателем (global predictor, 4096 записей по 3 бита) и 12-битным "путем истории" (history path). Оба алгоритма работали независимо, и если локальный отслеживал каждый отдельный условный переход, то глобальный -- последовательности переходов. Общий предсказатель ветвлений анализировал результаты обоих алгоритмов, и делал выводы в виде отдельной таблицы выборочного предсказателя (choice predictor, 4096 записей по 2 бита), на основе которой выводились предпочтения при расхождении локальных и глобальных прогнозов. Такой кооперативный метод позволял добиться лучших результатов, чем применение любого из подходов в отдельности.

При разработке EV6, учитывая большое число и сложность организации взаимодействия функциональных устройств, была полностью переработана схема расположения генераторов тактовых частот. Более равномерное распространение тактового сигнала позволило ядру работать на частотах, равных частотам куда более простого ядра EV56, при использовании того же техпроцесса. В общем, потребляемая чатотными генераторами мощность составляла для EV6 около 32% от общего потребления ядра; для сравнения, у EV56 этот показатель был около 25%, у EV5 -- около 37%, у EV4 -- около 40%.

Физически EV6 производился по той же 6-слойной 0,35µ CMOS6 технологии, что и EV56, состоял из 15,2 млн. транзисторов (из них около 9 млн. на I-cache, D-cache, и предсказатели переходов), имел площадь ядра в 314 кв.мм., и был рассчитан на рабочее напряжение от 2,1В до 2,3В. Тактовые частоты составляли от 466МГц до 600МГц (TDP прибл. от 80Вт до 110Вт). Форм-фактор: PGA-587 (Pin Grid Array).

В конце 1999 на рынок вышел 21264А (EV67), выполненный по 0,25µ CMOS7 техпроцессу от Samsung, с площадью ядра в 210 кв.мм., и пониженным рабочим напряжением в 2,0В. Никаких архитектурных изменений по сравнению с EV6 не наблюдалось. Тактовые частоты составили от 600МГц до 833МГц (TDP прибл. от 70Вт до 100Вт), что позволило Alpha вернуть лидерство на целочисленных операциях, незадолго до этого утраченное в пользу процессоров Intel и AMD.

В начале 2000 появились первые процессоры 21264B (EV68C), на этот раз от IBM, по 0,18µ CMOS8 техпроцессу с использованием медных проводников. Несмотря на прежнее отсутствие архитектурных изменений, многообещающая технология позволила поднять тактовые частоты сразу до 1250МГц. В 2001 Samsung смог наладить производство 21264B (EV68А) по своему 0,18µ техпроцессу, но с алюминиевыми проводниками, сократив площадь ядра до 125 кв.мм., и уменьшив напряжение питания до 1,7В, что позволило вывести тактовые частоты в диапазон от 750МГц до 940МГц (TDP прибл. от 60Вт до 75Вт).

В разных источниках проскакивали упоминания о 21264C и 21264D, с кодовыми именами EV68CB и EV68DC, выпускавшимися IBM по той же технологии, что и EV68C, и с теми же частотными характеристиками, поэтому их можно расматривать как частные варианты последнего. Единственным существенным отличием было использование нового форм-фактора, "безногого" CLGA-675 (Ceramic Land Grid Array) вместо PGA-587.

Для процессоров серии 21264 было спроектировано 2 чипсета: DEC Tsunami (21272; он же Typhoon) и AMD Irongate (AMD-751), хотя их могло бы быть значительно больше, ввиду того, что и 21264, и Athlon использовали почти одинаковую системную шину (она была лицензирована AMD ещё у DEC).

DEC Tsunami был чипсетом повышенной масштабируемости. На его основе проектировали как однопроцессорные, так двухпроцессорные и четырехпроцессорные системы, с разрядностью шины памяти от 128 до 512 бит (SDRAM ECC registered, 83МГц), поддержкой как одной, так и нескольких шин PCI (64-бит, 33МГц). Такой гибкости удалось достичь благодаря разделению чипсета на отдельные компоненты: контроллеры системной шины (C-chips, по одному на каждый процессор), контроллеры шины памяти (D-chips, по одному на каждые 64 бита ширины шины), и контроллеры шины PCI (P-chips, по одному на каждую требуемую шину). Поэтому ничего удивительного, что в некоторых системах (например, AlphaPC 264DP) чипсеты состояли из 12 микросхем...

Хотя AMD Irongate разрабатывался изначально как северный мост для материнских плат, предназначенных для процессоров Athlon, его также использовали в некоторых материнских платах для Alpha (например, UP1000 и UP1100). Так как он был одночиповым решением, то стоил намного дешевле DEC Tsunami и отличался существенно более низким энергопотреблением. Однако, его возможности не соответствовали потенциалу 21264 из-за отсутствия поддержки многопроцессорности и слишком узкой шины памяти (64-бит, SDRAM ECC unbuffered, 100МГц). Тем не менее, Irongate был первым чипсетом для Alpha с поддержкой шины AGP. И последним.

Часть 8. Эпоха Compaq

Судя по всему, Compaq приобрела остатки DEC из-за значительных сборочных мощностей, широкой сети дистрибьюции (в 98 странах) и кросс-лицензионного соглашения с Intel (позволяющего, например, выпускать 8-процессорные сервера линейки Profusion). Как показало дальнейшее развитие событий, подразделение по развитию архитектуры Alpha пришлось явно не к месту: Compaq издавна собирала рабочие станции и сервера на процессорах Intel, а также проявляла повышенный интерес и к процессорам AMD. Поэтому в июне 1998 Compaq вступилa в альянс с Samsung по развитию архитектуры Alpha (как известно, в феврале 1998 между DEC и Samsung было заключено соглашение, которое предоставляло последней доступ ко всем патентам по архитектуре Alpha, а также и позволяло выпускать уже разработанные DEC модели и даже проектировать собственные). Совместно была учреждена дочерняя компания, API (Alpha Processor Inc.), которая занималась маркетинговыми вопросами архитектуры (по-видимому, кто-то сделал нужные выводы из истории DEC). Летом 1998 системы на базе EV6 вступили в стадию массового производства, уверенно выигрывая по соотношению цена/производительность у имеющихся конкурентов. Серьёзные проблемы с выпуском будущего Itanium от Intel давали основание утверждать, что такое положение дел сохранится и в ближайшем будущем. Кроме Samsung, EV6 былa вынужденa производить сама Intel на Fab-6 в Хадсоне, по условиям договора с покойной DEC...

Год 1999 оказался неудачным для Compaq, в связи с падением объёмов продаж на рынке персональных компьютеров. Основной причиной называли недооценку возможностей, предоставляемых Интернетом для продаж компьютерной техники, и которыми активно воспользовалась Dell, перестроившая таким образом свою модель бизнеса, предлагая технику по самым низким среди крупных брэндов ценам. После финансовой катастрофы в 1-м квартале 1999 ушёл в отставку главный исполнительный менеджер Compaq, Экхард Пфайфер (Eckhard Pfeiffer). В целях экономии, Compaq начал сворачивать некоторые отрасли деятельности, и это отразилось на Alpha-системах: в мае 1999 было объявлено о закрытии сборочного цеха AlphaServer'ов в Салеме (Нью-Хэмпшир).

23 августа 1999 произошло довольно-таки знаменательное событие: Compaq отказалась от дальнейшего участия в разработке Windows NT, прекратила поставлять эту ОС со своими Alpha-системами и фактически в полном составе (примерно 120 человек) уволила группу программистов из бывшей Западной исследовательской лаборатории DEC (DECwest), работавших над этим проектом. Согласно статистике Compaq, среди всех предустановленных ОС на Alpha-системах Tru64 UNIX имела долю в 65%, OpenVMS -- в 35%, a на Windows NT приходилось около 5%, и поэтому дальнейшие работы над этой ОС не окупали себя. Неделю спустя Microsoft заявила, что отменяет работу над Windows 2000 для Alpha. Учитывая, что ещё в 1997 Microsoft свернула поддержку архитектур PowerPC и MIPS, будущее "универсальной ОС" свелось к одной-единственной архитектуре, если не считать IA-64...

Чтобы обеспечить лидерство архитектуры Alpha в обозримом будущем, в декабре 1999 Compaq и Samsung подписали меморандум, согласно которому обе компании инвестируют 500 млн. долл. США в развитие архитектуры Alpha (Samsung вложит 200 млн. в развитие и отладку новых техпроцессов, а Compaq использует 300 млн. на проектирование новых серверных решений, и на дальнейшее развитие Tru64 UNIX). Кроме того, в том же месяце Compaq и IBM заключили соглашение, согласно которому последняя будет производить процессоры Alpha с использованием своей технологии на медных проводниках, как только та будет отлажена; при этом Samsung всё же останется основным поставщиком процессоров Alpha. Если подводить итоги года для Compaq, то они довольно неплохо иллюстрировались курсом её акций: с 51 долл. США за шт. в феврале, и до 28 долл. США за шт. в декабре. Правда, многие аналитики утверждали, что могло быть и хуже.

Y2K обошелся для Compaq без потрясений. Samsung так и не успел наладить свой 0,18µ техпроцесс на алюминиевых проводниках, в отличие от IBM, которая начала ограниченные поставки EV68C для Compaq, а рынок был вынужден довольствоваться относительно медленными EV67. Разработка 21364 (ЕV7, также известный как Marvel) затянулась, хотя в анонсах уже значился 21464 (EV8, также известный как Arana). Крах dot-com'ов отразился и на курсе акций Compaq, упавшем к концу года до 15 долл. за шт., то есть на 44% по сравнению с началом года. Как ни странно, этот показатель можно считать отличным; другие компании, более зависящие от e-commerce, потеряли намного больше: Gateway -- 75%, Apple -- 71%, Dell -- 65%. Собственно dot-com'ы стали либо банкротами, либо были недалеки от этого; Yahoo.com потерял 95% своей рыночной стоимости, а Priceline.com -- 97%.

В начале 2001 Samsung смог наладить выпуск своих EV68А, но момент был упущен. Compaq планировала начать поставки систем с EV68C (AlphaServer'ов GS-класса), а также развернуть модернизацию имеющихся. EV7 был всё ещё где-то там, когда случилось то, чего мало кто ожидал: 25 июня 2001 (в "чёрный понедельник") Compaq объявила о постепенном переводе своих серверных решений с архитектуры Alpha на IA-64 к 2004. Работы над EV8 были отменены немедленно, хотя некоторые принципы его внутреннего устройства были опубликованы ещё на Microprocessor Forum в октябре 1999, а EV7 планировалось выпустить не ранее начала 2002, после чего Alpha Microprocessor Division подлежал расформированию, а основную часть его сотрудников должна была принять на работу Intel. Samsung и IBM вскоре прекратили производство процессоров Alpha. Далее события развивались ещё более драматично: 3 сентября 2001 Hewlett Packard заявила о своих намерениях приобрести Compaq, находящуюся в весьма сомнительном финансовом положении: к концу года курс её акций составил 10 долл. США за шт. Сделка была утверждена собраниями акционеров обеих компаний, а также правительствами США и Канады, и завершилась в мае 2002.

21 октября 2001 API, переименованная к тому времени в API NetWorks, передала все полномочия по поддержке (в том числе гарантийной) Alpha-систем компании Microway, крупнейшему [после Compaq] сборщику рабочих станций и серверов на архитектуре Alpha, старому партнёру DEC. Сама же API ушла с этого рынка, сконцентрировав внимание на сетевых технологиях, развитии шины HyperTransport и системах хранения данных.

В заключение можно сказать, что хотя Compaq и избежала многих ошибок, сделанных в своё время DEC, она так и не раскрыла весь потенциал архитектуры. Производительные Alpha-системы на 21264A и 21264B так и не попали в ценовую категорию до 2 тыс. долл. США, а бюджетный 21264PC так и не появился. Возможность массового выпуска недорогих материнских плат на основе AMD Irongate была проигнорирована, а стоимость DEC Tsunami, продаваемого Compaq по цене свыше 1000 долл. за шт. в оптовых партиях, не оставила Alpha-системам шансов на выход в средний ценовой диапазон. Другие производители чипсетов для AMD Athlon так и не адаптировали их для работы с 21264, хотя у VIA такое намерение изначально имелось.

Часть 9. EV7, EV79, EV7z, EV8

Первые новости об архитектуре процессора 21364 (EV7) прозвучали в октябре 1998 на Microprocessor Forum; уже тогда было известно, что процессор будет базироваться на ядре EV6, но с интегрированным контроллером Direct Rambus DRAM (предположительно, 4-канальным) и кэшем L2 (1,5Мб с 6-канальной ассоциативностью). Также прозвучало, что никаких изменений в ядре EV6 не планируется, хотя возможна и другая причина: разрабатывать было уже некому, так как штат инженеров-проектировщиков сократился довольно существенно. Ожидалось, что дизайн EV7 будет закончен к 2000.

После поглощения Compaq наследие в виде архитектуры Alpha было для HP ненужным довеском, так как она развивала свою 64-битную архитектуру PA-RISC (Precision Architecture RISC) и состояла в альянсе с Intel по разработке её 64-битной архитектуры IA-64 (то есть Itanium'а). Поэтому интерес HP в плане архитектуры Alpha ограничился сбытом и поддержкой унаследованных от Compaq линеек серверов на EV6/EV67/EV68, а также запуском в производство EV7, окончательно представленного в январе 2002.

Как и ожидалось, в основе EV7 лежало ядро EV68 (абсолютно без изменений) и несколько дополнительно интегрированных блоков: два контроллера памяти (два Z-box'а, для Direct Rambus DRAM PC800), многофункциональный маршрутизатор (R-box, для поддержки многопроцессорности и сетевых функций), и полноскоростной кэш L2 (S-cache, 1,75Мб с 7-канальной ассоциативностью). Разрядность шины данных к S-cache была как и у EV6 (128 бит), и собственно кэш работал со значительными задержками (12 тактов при чтении). Оба Z-box'а и R-box работали на 2/3 частоты ядра. Скорость работы каналов памяти зависела от Z-box'ов и составляла половину их частоты (соответственно, 1/3 частоты ядра), но с использованием технологии DDR.

Каждый Z-box поддерживал 5 каналов памяти (4 основных и 1 вспомогательный) разрядностью по 18 бит (16 для команд/данных/адресов, 2 для ECC). Вспомогательный канал был опцией, и мог использоваться для организации отказоустойчивого массива в памяти (приблизительно, как RAID3); к примеру, при записи в память учетверенного слова (quad-word, 64 бита) оно разделялось на 4 слова (word, 16 бит), каждое из которых отправлялось по своему каналу, а по вспомогательному записывалась контрольная сумма. Также, каждый Z-box мог держать до 1024 страниц памяти открытыми. Суммарная теоретическая пропускная способность подсистемы памяти одного EV7 составляла около 12Гб/с. Естественно, так как каждый EV7 в многопроцессорной системе располагал своей областью памяти, то такая модель памяти называлась NUMA (Non-Uniform Memory Access), в противовес к традиционному SMP (Symmetric Multi-Processing), в котором все установленные процессоры имели доступ к единой (общей) области памяти. Поэтому, каждый процессор в системе (из максимум 128) имел доступ к памяти как через свои контроллеры, так и через контроллеры других процессоров. Функцию связи между процессорами, как и между отдельно взятым процессором и локальной периферией, выполнял R-box. Он поддерживал 4 независимых канала с теоретической пропускной способностью в 6 Гб/с каждый (по одному на каждый подключенный соседний процессор), а также 1 дополнительный канал для скоростного ввода/вывода.

Так как EV7 внутренне унаследовал все интерфейсы EV6, то в процессоре должен был быть реализован блок поддержки системной шины последнего. Хотя эта часть процессора нигде не документировалась и даже не упоминалась, но определённые предположения касаемо её быстродействия всё же можно сделать. Так как минимальный рабочий коэффициент умножения у ядер EV6 был равен 3, то теоретическая пропускная способность магистрали к этому блоку составляла около 3Гб/с для EV7, что было в 4 раза ниже суммарных возможностей обоих Z-box'ов. Это было серьёзным аргументом в пользу того, что EV7 изначально задумывался для использования в многопроцессорных системах класса high-end.

Процессоры EV7 могли поключаться друг к другу по произвольным алгоритмам, но на практике использовались так называемые "torus" и "shuffle", причём второй был потенциально эффективнее в некоторых случаях (например, в 8-процессорной системе с алгоритмом подключения "shuffle" каждый процессор был непосредственно связан с 4 другими процессорами, а в случае с "torus" -- только с 3; нетрудно догадаться, что уже в 12-процессорной конфигурации этот аргумент отпадал).

Производился по 7-слойному 0,18µ CMOS8 техпроцессу, состоял из 152 млн. транзисторов (из них 137 млн. на I-cache, D-cache и S-cache), и, как следствие, имел огромную площадь ядра (397 кв.мм.). Частота экспериментальных образцов составила 1250МГц (155Вт TDP), хотя в производимых HP системах использовались процессоры с частотами от 1000МГц до 1150МГц. С инженерной точки зрения, EV7 заметно уступал предыдущим представителям архитектуры Alpha с точки зрения плотности размещения функциональных устройств на подложке, а поэтому нерационально использовал её площадь, что не замедлило отразиться на тактовых частотах и задержках при операциях с S-cache -- то есть, на производительности.

В декабре 2002 HP опубликовала пресс-релиз, в котором шла речь о появлении серверов на EV7 с частотой в 1150МГц уже в январе 2003, а вскоре должен был выйти EV79 (по 0,13µ SOI техпроцессу), и на этом развитие архитектуры должно было прекратиться. В марте 2003, на ISSCC'2003, был представлен прототип EV79, с площадью ядра в 251 кв.мм., рассчитанный на напряжение в 1,2В, и работающий на частоте в 1450МГц (100Вт TDP). Но уже в октябре 2003 появились первые новости о трудностях, связанных с производством EV79 на фабрике IBM, а ещё через полгода процессор был окончательно отменён.

В августе 2004 было объявлено o выпуске последнего процессора Alpha, EV7z с тактовой частотой в 1300МГц, на том же 0,18µ техпроцессе. Он был предназначен для установки исключительно в продукцию HP; также было заявлено, что сервера и рабочие станции архитектуры Alpha будут продаваться под маркой HP до 2006, а поддерживаться до 2011 года, но не более.

Отменённый 21464 (EV8) должен был быть дальнейшим развитием EV7, с удвоенным количеством основных функциональных устройств (8 целочисленных и 4 вещественных конвейера), и с увеличенным до 3Мб S-cache. Также была заявлена поддержка технологии SMT (Simultaneous Multi-Threading), которая должна была позволить одновременное выполнение (concurrent execution) до 4 программных потоков внутри одного ядра (возможно, эта технология была несколько родственной Intel HyperThreading). Площадь ядра прогнозировалась в 420 кв.мм. при 0,13µ SOI техпроцессе.

Эпилог

На момент написания статьи (апрель 2005) Alpha-системы всё ещё продавались, в основном через HP и Microway. Последняя даже предлагала относительно недорогие рабочие станции с 21164А и AlphaPC 164LX под Linux (за 2 тыс. долл. США в стандартной комплектации). Довольно значительное количество списанных (но все ещё работоспособных) рабочих станций и серверов, а также отдельных комплектующих, доступно через "онлайновые барахолки"; большинство этих систем прeдназначалось для работы с Windows NT, и на многие из них нельзя установить ни Digital UNIX, ни OpenVMS, а на некоторые даже *BSD (системы, не поддерживающие SRM console), хотя сохраняется возможность установки Linux из-под ARC/AlphaBIOS. Если вы имеете намерение приобрести Alpha-систему, выясните этот вопрос перед покупкой, чтоб не иметь впоследствии лишних проблем.

Согласно статистике, к июню 2001 только DEC и Compaq продали около 800 тыс. рабочих станций и серверов на Alpha. Точное количество систем, собранных и проданных другими компаниями, неизвестно, но эта цифра определённо превышает 500 тыс.

Многие утверждают, что архитектура Alpha умерла своей смертью. Надеюсь, после прочтения этой статьи у вас не останется сомнений, что её похоронили, причём заживо. Потому что так было выгодно.

История знает немало случаев, когда товар с худшими характеристиками вытеснял сопоставимый товар с лучшими техническими показателями. Возможно, первый товар стоил существенно дешевле второго. Также возможно, что второй товар продвигался на рынке существенно пассивнее первого. Или лицензионные отчисления были несопоставимы. Всё возможно. Не исключено, что маркетологи некоторых товаров, осознавая их ущербность, продвигают их на рынке наиболее агрессивно, понимая, что иначе их очередная зарплатa может оказаться последней. Одно очевидно: для успеха на рынке технические показатели того или иного продукта имеют далеко не самое первостепенное значение.

Жизнь продолжается...

Литература

1. Rich Witek, Dick Sites. Alpha Architecture Technical Summary, 1992.

2. Richard L. Sites. Alpha AXP Architecture, Digital Technical Journal, Vol. 4, No. 4, Special Issue, 1992.

3. Daniel W. Dobberpuhl, and others. A 200-MHz 64-bit Dual-issue CMOS Microprocessor, Digital Technical Journal, Vol. 4, No. 4, Special Issue, 1992.

4. Edward McLellan. The Alpha AXP Architecture and 21064 Processor, IEEE Micro, 1993.

5. Dina L. McKinney, and others. Digital's DECchip 21066: The First Cost-focused Alpha AXP chip, Digital Technical Journal, 1994.

6. Robert Couranz. The E2COTS System and Alpha AXP Technology: The New Computer Standard for Military Use, Digital Technical Journal, Vol. 6, No. 2, 1994.

7. Samyojita A. Nadkarni, and others. Development of Digital's PCI Chip Sets and Evaluation Kit for the DECchip 21064 Microprocessor, Digital Technical Journal, Vol. 6, No. 2, 1994.

8. Linley Gwennap. Digital Leads the Pack with 21164, Microprocessor Report, Vol. 8, No. 12, 1994.

9. William J. Bowhill, and others. Circuit Implementation of a 300-MHz 64-bit Second-generation CMOS Alpha CPU, Digital Technical Journal, Vol. 7, No. 1, 1995.

10. David P. Hunter, Eric B. Betts. Measured Effects of Adding Byte and Word Instructions to the Alpha Architecture, Digital Technical Journal, Vol. 8, No. 4, 1996.

11. Linley Gwennap. Digital, MIPS Add Multimedia Extensions, Microprocessor Report, Vol. 10, No. 15, 1996.

12. Daniel Leibholz, Rahul Razdan. The Alpha 21264: A 500 MHz Out-of-Order Execution Microprocessor, Proceedings of of IEEE COMPCON'97, 1997.

13. Michael K. Gowan, Larry L. Biro, Daniel B. Jackson. Power Considerations in the Design of the Alpha 21264 Microprocessor, DAC 98, June 15-19, 1998.

14. Linley Gwennap. Compaq, Intel Fight Digital Brain Drain, Microprocesor Report, Vol. 12, No. 14, October 26, 1998.

15. Linley Gwennap. Alpha 21364 to Ease Memory Bottleneck, Microprocessor Report, Vol. 12, No. 14, October 26, 1998.

16. M. Matson, and others. Circuit Implementation of a 600 MHz Superscalar RISC Microprocessor, Compaq Technology Journal, 1998.

17. Chart Watch: Workstation Processors, Microprocessor Report, May 10, 1999.

18. Daniel W. Bailey. High-Performance Alpha Microprocessor Design, Compaq Computer Corporation, 1999.

19. Exploring Alpha Power for Technical Computing, Compaq Technology Brief, April 2000.

20. Zarka Cvetanovic. Performance Analysis of the Alpha 21364-based HP GS1280 Multiprocessor, Hewlett-Packard Corporation, 2002.

21. Kevin Krewell. Alpha EV7 Processor: A High-Performance Tradition Continues, Microprocessor Report, April 5, 2002.

22. Ronald P. Preston. Design of an 8-wide Superscalar RISC Microprocessor with Simultaneous Multihreading, Compaq Computer Corporation, ISSCC Report, 2002.

23. Peter N. Glaskowsky. Moore, Moore, and More at ISSCC, Microprocessor Report, March 23, 2003.

Также использовалась многочисленная техническая документация от DEC и Compaq, без использования которой эта статья была бы неполной.

Автор выражает благодарность Wikipedia за информацию по ранней истории DEC, равно как и её продукции того времени, а также Терри Шеннону (Terry Shannon) за регулярные и содержательные публикации его издания "Shannon Knows {DEC, Compaq, HPC}"

В статье были использованы материалы многих неофициальных Интернет-ресурсов, список которых слишком длинен, чтобы быть именованным ниже; их авторам выражается большая и искренняя признательность за особенно интересные факты, комментарии, точки зрения, и т.д.

Фотографии EV4 и EV6 предоставлены cpu-collector.com

Особая благодарность за дельные примечания и пожелания в ходе подготовки статьи к печати выражается ISA_user, VLev, Yury_Malich, Stranger_NN, и конечно же, matik!