Ваш город: Москва

Transmeta Efficeon

Эпиграф: «Бизон полез на дерево, и сначала дело у него ладилось, но на высоте

десяти футов он споткнулся и соскользнул вниз. Я вздохнул с облегчением.

Он опять полез - взобрался немного повыше - и опять соскользнул. Однако

он снова попробовал и на этот раз действовал осмотрительно»

Mark Twain, Roughing It, 1872

Вступление

Некоторое время наблюдая за ходом дел в Transmeta, начинаешь замечать, что пути становления компании постоянно усеяны какими-то терниями: то сами процессоры по каким-то причинам доводятся "до кондиции" слишком долго, то подводят смежники в лице OEM-изготовителя чипов, то сама компания, объявив поддержку чего-только-можно-выдумать, включая встроенное шифрование данных, по неизъяснимым причинам пропадает из новостных лент на полгода.

Анонс процессорного ядра с новым именем Transmeta Efficeon, состоявшийся осенью прошлого года, не стал исключением: прошло, как минимум, полгода с начала поставок этих процессоров, более того, особо приближенные даже успели потрогать руками второе поколение этих чипов, а о массовости Efficeon до сих пор нет и речи. Винить в этом можно кого угодно: нерасторопного разработчика, нынешнего производственного партнера - тайваньскую TSMC, однако, мне кажется, что в первую очередь стоит вспомнить о "калибре" Transmeta: не думаю, что стоит требовать от компании с капитализацией немногим более $100 млн. и ежеквартальными убытками уровня $20 млн. прыти лидеров процессорного рынка. Впрочем, такая извинительная позиция со временем может пребольно ударить по самой Transmeta, ибо диалектика ситуации заключается в том, что никто в наше время не собирается ждать отстающих, и, если не использовать дизайн чипа в предназначенный для него отрезок "рыночной жизни", его можно смело сдавать в кунсткамеру, к другим смелым и оригинальным, но так и не нашедшим практического применения изобретениям.

Почему обзорами архитектуры Efficeon не усыпан сплошь и рядом Рунет и даже английский сегмент Сети? Увы, дело не только в малой распространенности этих чипов и определенной недоступности образцов для тестирования. Беда также в том, что сама Transmeta, возможно, ввиду экономии средств, занимается активным продвижением и популяризацией процессора в основном в Японии. Соответственно, все подробности о разработке новых чипов от Transmeta относительно стабильно публикуются в японских изданиях и лишь изредка, в "выщипанном" поверхностном виде – в англоязычной прессе. Сайт компании, как правило, представляет лишь поверхностные данные о своей продукции, уровень и оперативность подачи информации можно назвать достаточной, пожалуй, лишь для толстых глянцевых журналов, где достаточно показать фото красивого ноутбука, а также снимок улыбающегося вице-президента и CTO компании Дэвида Дитцеля (David Ditzel) с чипом серии TM8000, зажатым между указательным и большим пальцем. :-)

Ввиду того, что основные сведения о внутреннем строении процессоров Efficeon, особенно, о принципе их работы, отрывочны и почерпнуты из самых разнообразных источников, обращаюсь к экспертам: за возможные недоговорки или обобщения, имеющиеся в описании, просьба особо не пинать. :-)

Общие сведения

Итак, начнем с событий середины октября 2003 года, когда в дни проведения конференции Microprocessor Forum 2003 компания Transmeta наконец-то решилась представить первую информацию о новом поколении своих процессоров с названием Efficeon.

Трудно вспомнить другой процессор, который еще до своего "рождения" пережил столько "рабочих" имен. На заре эпохи начала разработки чипа, примерно пять лет назад, его окрестили легко и непринужденно, по аналогии с предыдущей серией чипов – Crusoe TM8000. В последствии, процессор получил имя Astro, под которым "проходил" без малого год (кстати, немногие помнят, что имя было дано новому процессору в честь пса Astro из знаменитого в прошлом мультсериала The Jetsons. :-) А Вы о чем подумали?).

Наконец, в августе 2003 года в Transmeta решили, что на фоне свежевыдуманных неологизмов типа Centrino или Opteron классическое имя Astro будет не слишком модным, и новичку "выдали" такое же синтетическое имечко – Efficeon, под которым он и появился на рынке.

Чтобы рассказ о специфике архитектуры процессоров Efficeon был воспринят в правильном ключе, думаю, с самого начала стоит отметить, что чип разрабатывался как основа для построения ультрапортативных ноутбуков, а также бесшумных планшетных ПК и других экономичных бытовых электронных устройств. Впрочем, окрыленная успехом своей предыдущей серии, Crusoe TM5800, Transmeta теперь уверенно продвигает свои новые чипы также для работы в составе blade-серверов, тонких клиентов, всевозможных встраиваемых систем.

В соответствии с поставленными требованиями перед разработчиками было сформулировано техническое задание: создать очень экономичный и в меру производительный чип - наследник Crusoe, с максимальной интеграцией, для систем без принудительного охлаждения, со всевозможными современными функциональными расширениями. Таким образом, на свет явился прототип семейства Efficeon, TM8000.

Процессоры серии TM8000, впрочем, как и другие чипы от Transmeta, нельзя рассматривать как аппаратное решение в чистом виде. По сути, Efficeon является симбиозом аппаратного VLIW (Very Long Instruction Word) ядра с так называемым "кодоморфным" (Code Morphing Software, или сокращенно CMS) программным обеспечением, осуществляющим преобразование команд формата x86 во внутренние VLIW-слова. Основным отличием чипов серии TM8000 можно назвать то, что они имеют 256-битное внутреннее представление данных и способны исполнять до восьми инструкций за такт, в отличие от своих предшественников Crusoe TM5x00 со 128-битным внутренним представлением и четырьмя инструкциями за такт. Подробнее о принципе работы этого механизма мы поговорим позже.

Функционально, в первом приближении, чип Efficeon можно разделить на следующие блоки:

Процессорное ядро

Кэш данных и кэш инструкций L1

Кэш L2

Интегрированный в CPU северный мост

Интегрированный контроллер 64-битной памяти, поддержка до 4 ГБ DDR400

Опционально - поддержка ECC

Интегрированная шина AGP спецификаций 2.0, поддержка режимов AGP 1x, AGP 2x, AGP 4x

Внутренний транспортный интерфейс для связи с южным мостом: 8-битная двунаправленная шина HyperTransport (интегрированный в процессор point-to-point интерфейс LVDS), производительность до 1.6 ГБ/с

Модуль контроля терморежима и энергопотребления

Специальная интегрированная шина LPC (Low Pin Count) 1.0

Несколько слов о миссии интерфейса LPC ROM. 5-контактная шина LPC предназначена для скоростного доступа к кодоморфному ПО и BIOS. Шина LPC процессоров TM8300/TM8600 работает на тактовой частоте 33 МГц, используется при инициализации и загрузке системы. В процессе начальной инициализации системы кодоморфное ПО, хранящееся в архивированном виде в LPC ROM, разархивируется в память DDR и находится в ней постоянно, занимая некоторый ее объем. Точные данные о размерах области, отведенной в оперативной памяти под CMS, толком нигде не указываются, хотя, один из японских источников со ссылкой на м-ра Дитцеля как-то намекал на 32 Мб. Там же содержался прозрачный намек на то, что для систем на процессорах Efficeon весьма желателен объем оперативной памяти никак не меньше 512 Мб.

Разумеется, участок DDR памяти, зарезервированный под кодоморфное ПО, невидим для кода x86. С помощью интерфейса LPC также производится перепрошивка BIOS и новых версий кодоморфного ПО (CMS).

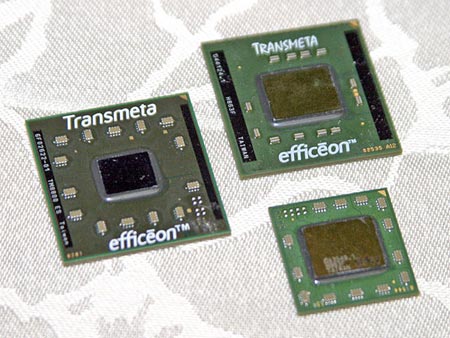

Во времена анонса TM8600 предполагалось, что уже первое поколение чипов, выполненное с нормами 0.13 мкм техпроцесса, с места в карьер будет явлено сразу в трех модификациях – стандартной базовой TM8600, недорогой усеченной TM8300 и в миниатюрном корпусе, TM8620. Увы, жизнь расставила акценты по другому, к настоящему времени из этого поколения мы имеем лишь более-менее массовые TM8600 в ноутбуках от Sharp, нескольких концептуальных разработках blade-серверов и встраиваемых систем, плюс компактные TM8620 в штучных количествах. Впрочем, если следовать широко распространенной теории о том, что процессоры с уполовиненным кэшем L2 получаются после отбраковки "некондиционных" кристаллов, становится понятным, почему чип TM8300 - своеобразный "Celeron от Transmeta", так и не появился на рынке: слишком мало для этого было выпущено TM8600. Для чистоты рассказа приведем спецификации всех трех версий процессорных ядер.

Как видно из таблицы, ядро Efficeon, выполненное с соблюдением норм 0,13 мкм техпроцесса на базе 80 млн. транзисторов, имеет площадь 119 кв. мм. Много это или мало? Для сравнения: площадь ядра 0,13 мкм процессора TM5800 с 512 КБ кэша L2 составляет 55 кв. мм, у 90 нм ядра Intel Dothan с его 144 млн. транзисторов площадь ядра составляет 87 кв. мм, но у "настольного" ядра Northwood, выполненного на 55 млн. транзисторов, площадь равна 131 кв. мм.

В таких пределах компанией Transmeta было декларировано энергопотребление чипов Efficeon первого поколения:

Впрочем, все версии, кроме 1.0 ГГц варианта, долгое время остались мифом; в начале 2004 года в Сети мелькали разрозненные слухи о выходе 1.1 ГГц чипа, однако в массовых поставках они появились лишь к лету. На этот случай у меня также есть масса теорий, однако, наиболее вероятной из них видится отсутствие целесообразности производства 7 Вт чипа на фоне начавшихся к тому времени массовых поставок ULV/LV версий чипов Pentium M. Также весьма вероятно, что Transmeta уже зимой сконцентрировала свои скудные финансовые потоки на инвестициях в портирование архитектуры Efficeon на 90 нм техпроцесс. В момент написания этого материала на сайте компании процессоры Efficeon TM8600 и TM8620 позиционировались с тактовыми частотами в диапазоне 1.0 ГГц – 1.2 ГГц.

Как известно, все чипы Efficeon первого поколения производились, производятся и будут производиться на 0,13 мкм линиях традиционного производственного партнера, тайваньской компании TSMC. Интересно в этой связи отметить, что даже после сообщения об успешном получении опытных партий процессоров Efficeon второго поколения, выполненных на производственных линиях Fujitsu, Transmeta не планирует отказываться от услуг TSMC и по-прежнему намерена заказывать у нее 0.13 мкм чипы серии TM8600.

Очевидно, что при организации более-менее массового производства есть шансы снизить себестоимость одного процессора, и в таком случае недорогие чипы с энергопотреблением до 7 Вт придутся к месту, например, на рынках субноутбуков с диагоналями экранов порядка 10,4 дюймов и менее, а также blade-серверов и встраиваемых систем. Впрочем, как это иногда бывает, пронырливые производители успели заметить достаточно выгодное сочетание продвигаемого VIA Technologies (для создания миниатюрных ПК и развлекательных центров) форм-фактора Mini-ITX и процессора Efficeon, пока что более интересного, чем VIA Antaur, в результате чего на японском рынке уже не редкость вот такие системные платы класса MB860 от IBASE Technology в комплекте с 1.2 ГГц чипами TM8600:

Начало производства второго поколения чипов Efficeon, похоже, состоится в рамках намеченного графика - во втором полугодии 2004, но уже на линиях нового производственного партнера, японской Fujitsu, с соблюдением технологических норм 90 нм техпроцесса. По крайней мере, первые образцы чипов были получены еще в конце апреля, а уже в июне Transmeta смогла продемонстрировать рабочие образцы процессора Efficeon TM8800. Нынешняя ревизия ядра - третья по счету, позволила запустить его на тактовой частоте 1.6 ГГц, при этом, на стенде компании в рамках выставки Computex 2004, где Transmeta демонстрировала этот чип, система работала без активного охлаждения, с обычным радиатором, что позволяет сделать выводы о благополучном выходе на расчетный TDP порядка 7 Вт. Таким образом, сохраняется надежда, что компания также сможет представить 90 нм чипы с TDP порядка 3 Вт и 5 Вт, с тактовыми частотами 1 ГГц и 1.4 ГГц соответственно.

Как и прежнее поколение процессоров Efficeon, серия TM8800 в перспективе будет представлена тремя моделями, отличия которых вкратце сведены в таблицу ниже.

Что касается архитектуры ядра, то она изменилась незначительно, практически, исключительно благодаря применению новой версии кодоморфного ПО CMS. Таким образом чип "обзавелся" поддержкой расширенного набора команд SSE3 и новой аппаратной функции, антивирусной защиты NX (Microsoft Windows XP, после установки ServicePack2), которой, кстати, еще нет в ядре Dothan.

В целом же серию TM8800 можно охарактеризовать как редизайн с целью портирования ядра на 90 нм техпроцесс, преследующий цель снижения энергопотребления чипа при одновременном увеличении производительности за счет роста тактовой частоты. Также не исключено, что использование 90 нм техпроцесса позволит снизить себестоимость серии Efficeon, так как выпуск TM8800, имеющего площадь кристалла всего 68 кв. мм, на 300 мм пластинах выглядит гораздо привлекательнее опытов с первым поколением чипов. Что касается уровня предполагаемого энергопотребления процессоров серии TM8800, он сведен в таблице ниже, и на данном временном отрезке выглядит вполне привлекательно.

Правда, привлекательность TDP второго поколения чипов Efficeon будет сохраняться до тех пор, пока у Intel (ориентировочно – в третьем квартале 2004 года) не появятся ULV чипы Pentium M 733 с ядром Dothan и тактовой частотой 1.10 ГГц, TDP которых составит всего лишь 5 Вт. Далее, в начале 2005 года Intel планирует выпустить ULV модель Pentium M 753 с тактовой частотой 1.20 ГГц примерно с таким же TDP. По крайней мере, пока что шансы вырваться на оперативный простор у Transmeta остаются - в случае, если компания не будет мешкать с массовым выпуском своего 1.6 ГГц Efficeon. В ином раскладе, к Новому году они просто могут в очередной раз стать историей или, в лучшем случае, очередным нишевым продуктом.

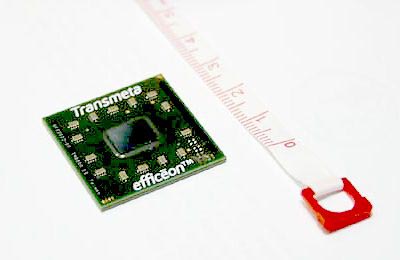

Кстати, малогабаритный вариант чипа Efficeon первого поколения, TM8620, был впервые продемонстрирован на Computex 2004, вместе с анонсом второго поколения процессоров. Миниатюрная версия процессора выполнена в 592-контактном корпусе OBGA с шагом контактов 0.8 мм, будет производиться с тактовыми частотами от 900 МГц до 1,1 ГГц на мощностях прежнего партнера, TSMC, с соблюдением норм 0.13 мкм техпроцесса.

Конечно же, Transmeta не обходится без традиционных "наездов" на платформу Intel Centrino, ибо сравнивать свои чипы с чем-то надо. Например, старательно подчеркивается, что крохотный TM8620 в связке с южным мостом ULi M1562S (имеется в виду старый добрый M1562 в корпусе уменьшенных размеров) и графическим ядром ATI MOBILITY RADEON занимает всего 1886 кв. мм, в то время как аналогичный комплект из Pentium M (35 х 35 мм) в связке с северным интегрированным (37,5 х 37,5 мм) и южным (31 х 31 мм) мостами занимает порядка 3592 кв. мм. Кстати, в случае с 90 нм чипом TM8800 ожидается переход на использование южного моста ULi M1563S габаритами 23 x 23 мм (уменьшенной версии прежнего M1563).

Концептуальная плата на базе Efficeon TM8620 + ULi M1562S + ATI MOBILITY RADEON

Кстати, системы на базе процессоров Efficeon, помимо традиционного 3D "сопровождения" от ATI, будут также комплектоваться графическими решениями на чипах серии Volari XP5 от XGI Technologies. По крайней мере, к июню компании объявили о завершении процесса адаптации графики XGI для платформы Efficeon TM8600 и о скором окончании тестирования XP5 в связке с новым 90 нм чипом TM8800. Напомню, серия XP5, доставшаяся Volari по наследству после покупки графического подразделения Trident, выполнена на базе известной линейки мобильных чипов XP4 и состоит из трех версий: Volari XP5 для массовых мобильных ПК, XP5m32 и Volari XP5m64, с интегрированными 32 МБ и 64 МБ памяти DDR, для легких и производительных ноутбуков соответственно.

Чипы серии Volari XP5 поддерживают интерфейс до AGP 8x (хотя в случае с Efficeon с его интегрированным портом AGP 4x это не пригодится), работают на тактовых частотах до 250 МГц и поддерживают до 128 МБ 128-битной памяти DDR с частотой до 250 МГц в организации 8Mx32, 4Mx32, 16Mx16, 8Mx16 and 4Mx16. Ядро BrightPixel обладает 4-конвейерным движком с двумя независимыми пиксельными конвейерами, есть аппаратная поддержка DirectX 8.1 при программной совместимости с DirectX 9.0. Ядро Volari XP5 состоит из 25 млн. транзисторов, изготавливается с соблюдением 0.13 мкм CMOS техпроцесса, выполнено в 612-контактном корпусе BGA габаритами 31 х 31 мм. Чип обладает максимальным энергопотреблением до 3.5 Вт, при этом благодаря встроенному двухканальному LVDS трансиверу поддерживается вывод на дисплеи с разрешением до UXGA (1600 x 1200), а 350 МГц RAMDAC обеспечивает вывод на CRT дисплеи с разрешением до 2048 x 1536.

В целом, задумка выглядит недурственно, если все пойдет согласно планам. Дальше расписывать в подробностях перспективы "победного шествия" процессоров Efficeon не вижу смысла, уж больно часто последнее время срываются планы производителей, даже на ближайшие полгода-год. Поэтому, для завершения разговора о перспективах просто приведу скриншот-роадмэп из презентации Transmeta, где схематически присутствует даже третье поколение чипов:

Пожалуй, на этом наш краткий экскурс в технологические особенности платформы Efficeon можно считать законченным. Самое время перейти к описанию особенностей архитектурных. Поскольку различия между первым и вторым поколением весьма умозрительны и, главным образом, заключаются в применении версий CMS, далее термином Efficeon будут обозначаться новые процессоры без разделения на поколения. В случае, когда это понадобится, проще будет называть их по рыночным именам: соответственно, TM8600 в случае первого поколения и TM8800 в случае второго.

Архитектура

Само название нового ядра, выдуманное в Transmeta - "Efficeon", является составным из двух – "Effi", то есть, "эффективный" и "Eon" (Era, "эра"), и призвано подчеркнуть эффективность новой архитектуры, разумное сочетание энергопотребления, тактовой частоты, количества транзисторов и производительности – тенденция, надо отметить, нынче общая для всех производителей центральных и графических процессоров.

Как известно, процессорные ядра от компании Transmeta, предтечей которых можно назвать разработанный в Sun в конце 1999 года, но так и не рожденный в "железе" процессор MAJC (Microprocessor Architecture for Java Computing; впрочем, "мертворожденность" – стабильный удел процессоров, заточенных под определенный язык), традиционно строятся на архитектуре так называемого сверхдлинного командного слова - VLIW (Very Long Instruction Word). Набор команд архитектуры x86 не является "родным" для такого процессора, и для его выполнения между процессором с архитектурой VLIW и стандартным для всех x86 систем BIOS вводится своеобразный программный слой, который как раз и занимается ретрансляцией кода x86 в "длинные слова" чипов Crusoe/Efficeon.

Таким образом, в отличие от CISC-архитектур (или подмножества "RISC-inside CISC-outside"), характерных для большинства нынешних чипов с архитектурой IA-32, компания Transmeta избрала для своих процессоров сочетание ядра с архитектурой VLIW и программного "кодоморфного" (Code Morphing Software, CMS) динамичного компилятора - этакого дизассемблера для "общения" с внешними инструкциями IA-32. При этом, фактически получилось так, что транслятор кода, блок предсказания ветвлений и принцип внеочередного исполнения инструкций сохранились, но теперь "вынесены" за пределы аппаратной части чипа в программное окружение, которое с успехом справляется со всеми этими функциями в реальном времени. Разумеется, расплата за это неизбежна, в случае с чипами от Transmeta приходится мириться с тем, что кодоморфное ПО делит аппаратные ресурсы и циклы процессора как минимум, с x86 приложениями и операционной системой.

Постепенно вводя читателей в подробности работы процессорного ядра Efficeon, попробую проиллюстрировать иерархию обычной x86-системы и версии от Transmeta следующей схемой:

Обратите внимание: кодоморфное программное обеспечение CMS играет роль своеобразного "ретранслятора" команд x86 во внутренние VLIW-слова чипа Efficeon. При этом процесс является динамическим, трансляция производится "на лету". Преимущества такой организации налицо: оптимизированная версия "IA32-ретранслятора" со временем может быть с легкостью переписана и прошита как обычное firmware в флэш-память. Понадобилось добавить, например, поддержку SSE3 или других дополнительных инструкций – никаких проблем, похожих на выпуск новой ревизии или даже поколения процессоров у других производителей x86-чипов не будет, просто "заливаем" для Efficeon новую версию CMS – и все дела.

Однако, диалектическая "палка о двух концах" сильно "стукнет" по производительности такого процессора в случае недостаточной оптимизации кодоморфного ПО. Разумеется, в подобном тандеме суммарное быстродействие процессора значительным образом зависит от качества компилятора, оптимизирующего последовательности операций.

Не особенно вдаваясь в особенности VLIW-архитектуры в рамках этой статьи, хотелось бы все же отметить, что из основных "магистральных" путей увеличения быстродействия подобных процессоров можно отметить два: подъем тактовой частоты ядра вкупе с конвейеризацией обработки операций, или увеличение количества операций, выполняемых за один машинный такт. Transmeta по мере возможностей пробует "прорваться" на обоих фронтах.

Итак, новый процессор работает с внутренними инструкциями длиной 256 бит, в то время как предыдущие чипы серий Crusoe оперируют 128-битными VLIW-словами. Очевидно, что при разумной организации процесса такого "демультиплексирования" в сочетании с подъемом тактовых частот у новых поколений чипов можно добиться многого, хотя линейного удвоения производительности, как мы убедимся ниже, все же не получится – чудес на свете не бывает.

Сразу же необходимо выделить главное отличие принципа использования кодоморфного ПО от работы привычных процессоров x86: в случае с процессорами от Transmeta софт CMS способен транслировать x86 инструкции группами, в то время как суперскалярные чипы транслируют по одной обособленной x86 инструкции. Более того, в то время как традиционные x86 архитектуры обрабатывают каждую x86 инструкцию каждый раз по мере ее востребованности, кодоморфное ПО от Transmeta, однажды транслировав инструкцию, сохраняет результат в кэше трансляции, и в следующий раз, когда попадается уже транслированный участок x86 кода, система "пропускает" стадию трансляции, применяя уже однажды оптимизированный код.

Переходим к самому важному этапу – процессу формирования VLIW-слова из x86 инструкций. Несмотря на то, что с момента анонса нового ядра Transmeta прошло более полугода, процесс этот в печати толком до сих пор не освещен, более того, даже работа прежнего ядра Crusoe описана до сих пор поверхностно, за исключением редких "островков" подробностей в японо-язычной печати.

Помимо удвоения длины VLIW-слова, VLIW-ядро процессоров Efficeon также содержит более чем вдвое увеличенное число исполнительных модулей – одиннадцать (по числу – как у Itanium 2), против пяти у Crusoe:

Два модуля Load/Store (Load/Store/32bit add)

Два модуля ALU для работы с целочисленными данными (Integer ALU)

Модуль адресации (Address Alias Checker)

Модуль для работы с FP/SSE/SSE2/MMX

Модуль для работы с SSE/SSE2/MMX

Модуль ветвлений (Branch)

Вспомогательные модули (2 x Exec, 1 x Control)

В результате ядро Efficeon обладает теми же двумя модулями работы с целочисленными данными, что и Crusoe, однако, количество модулей Load/Store у нового ядра удвоилось. В добавок к этому, число модулей обработки FP/SIMD данных удвоилось, и появилась поддержка SSE/SSE2, которой не было у Crusoe. Также обратите внимание на появление специфического аппаратного модуля - Address Alias Checking, имеющего схожую реализацию в архитектуре IA-64 и впервые выделенного в ядре Efficeon в отдельный самостоятельный блок.

К сожалению, более-менее вразумительных данных о функциональном назначении модулей Exec и Control до сих пор нет.

Что касается структуры конвейерной организации ядра Efficeon, в целом она осталась практически неизменной со времен Crusoe: 6-стадийный конвейер для целочисленных данных, 6-стадийный конвейер для данных с плавающей точкой и 6-стадийный конвейер для операций Load/Store. Вот таким образом выглядит структура организации конвейеров:

В отличие от процессора Crusoe, обрабатывавшего 64-битные (две инструкции) или 128-битные (четыре инструкции, по одной каждого типа) слова, в ядре Efficeon структура VLIW-слова расширилась до 256-битного формата (восемь инструкций). Постепенно мы подобрались к одному из основных отличий нового процессора от своих предшественников: ядро Efficeon включает в себя шестьдесят четыре 32-битных целочисленных регистра и шестьдесят четыре 80-битных регистра для обработки данных с плавающей точкой, по 48 регистров из каждой группы обладают функциональностью так называемого "теневого регистра" (shadow register).

В отличие от Crusoe, Efficeon также обзавелся четырьмя дополнительными предикативными регистрами, схожими по функциональности с имеющимися у IA-64 чипов Itanium. Ассоциативный буфер трансляции (TLB, Translation Look-aside Buffer) процессора Efficeon обладает битами защиты и схемой отображения адресации, сходной с x86 процессорами.

Кому-то может показаться, что такая организация менее гибка, нежели работа с группами инструкций с переменной длиной, ведь таким образом снижается степень совместимости (что, впрочем, является типичной особенностью VLIW архитектуры). Однако, в отличие от аппаратных трансляторов классических VLIW-процессоров, кодоморфное ПО CMS не имеет столь жесткой привязки к ядру, и на степень совместимости поколений процессоров можно в целом наплевать. Яркий тому пример: предыдущие поколения процессоров от Transmeta, TM3200 и TM5400, отнюдь не были совместимы друг с другом на бинарном уровне.

Как мы уже выяснили, за каждый такт процессор Efficeon может "успеть обслужить" от одного до восьми модулей. В компании Transmeta очень любят сравнивать 256-битное VLIW-слово процессора Efficeon с "молекулой", состоящей, соответственно, из восьми "атомов". На деле процесс происходит следующим образом: на программном уровне обновленное к выпуску Efficeon программное обеспечение CMS преобразует инструкции x86 в 3-операндные RISC-подобные команды (атомы) с фиксированной 32-битной длиной, которые затем комбинируются в 256-битные параллельные VLIW-пакеты (молекулы), от одной до восьми инструкций в параллель. Таким образом, подаваемая на VLIW-ядро процессора последовательность 256-битных команд является ни чем иным как списком из этих самых "молекул". Ядро чипа при такой организации вовсе не "заморачивается" порядком исполнения команд или предсказанием их очередности, его основная и единственная задача – "прогонять" последовательность молекул с максимально возможной скоростью.

256-битное ядро Efficeon позволяет исполнять до восьми 32-битных команд-атомов за один цикл. Какое количество реальных атомов попадает в такую молекулу – это уже вопрос "добросовестности" CMS-компилятора, может быть записана лишь одна команда, могут быть "заполнены" и все восемь "посадочных мест" этой 256-битной молекулы. Именно за счет того, что все сложности управления процессом трансляции x86 кода возложены на программную часть, удалось упростить внутреннюю VLIW-архитектуру ядра донельзя, ограничившись использованием 6-стадийного конвейера для целочисленных данных и 8-стадийным конвейером для данных с плавающей точкой. Собственно говоря, именно благодаря рационализации аппаратной части процессорного ядра и управляющей логики стало возможным значительное снижение соотношения производительность / энергопотребление у процессоров этой серии.

Итак, мы включили систему, на этапе первоначальной инициализации программа CMS разархивирована из Flash ROM в оперативную память, начинается обработка x86 кода. Весь процесс трансляции и исполнения кода CMS разбит на четыре фазы, которые в Transmeta называют "Gears", или "шестеренки". Для сравнения: ретрансляция кода в Crusoe происходила в два захода.

В первой фазе "первая шестеренка" CMS занимается профилированием процесса исполнения кода x86. Действие подразумевает под собой сбор кодоморфным ПО информации для анализа потоков, ветвления данных и классификации функций Load/Store (I/O vs память). Например, целочисленное арифметическое действие, включающее операцию загрузки из памяти, дизассемблируется на атом целочисленного арифметического действия и атом загрузки.

Основная оптимизация кода производится на втором и третьем этапе "прохода" CMS-компилятора. Вторая "шестеренка" (2nd Gear) разделяет на атомы до ста x86 инструкций, выстраивает очереди на их параллельное исполнение, производит частичную оптимизацию.

Следующая, третья "шестеренка" (3rd Gear) шлифует и улучшает оптимизацию, главным образом, часто используемых фрагментов кода. На этом этапе фактически формируется в общих чертах конечный VLIW-код.

Заключительная, четвертая фаза (4th Gear) посвящена оптимизации наиболее сложных участков кода, "сращиванию" отдельных регионов, уже оптимизированных на предыдущих этапах, максимальному распараллеливанию кода (для достижения полной загрузки 256-битного слова полезным кодом). На этой финальной стадии преобразования кода кодоморфное ПО просматривает получившийся код "с высоты птичьего полета", идентифицируя и оптимизируя наиболее сложные участки.

Впрочем, все так гладко лишь на бумаге. Две главные проблемы, которые присущи подобному типу формирования команд, заключаются в высокой требовательности к размеру и быстродействию кэш-памяти, с помощью которой производится обработка бинарного кода. Вторая проблема заключается в том, что полное заполнение 256-битного слова достигается не всегда. Известно, что 32-битные атомы, возникающие в результате преобразования x86 кода, "наполняют" 256-битное VLIW-слово по одному, два, три и более – до восьми в идеальном случае. Возможность "наполнения" 256-битного VLIW-слова различным количеством атомов, вдвое большим нежели у чипов серии Crusoe – безусловный плюс ядра Efficeon, однако, в случае наполнения команды небольшим количеством "атомов" эффективность такого преобразования здорово падает. Разумеется, и в этом случае эффективность работы процессора целиком и полностью ложится на программную часть процессора, CMS. Впрочем, в этом заключается и гибкость организации VILW-архитектуры, так как CMS-компилятор всегда можно обновить.

Система управления питанием и терморежимом. Технология LongRun

Процессоры семейства Efficeon поддерживают режимы системы управления питанием ACPI с помощью все того же кодоморфного ПО. Экономия энергопотребления осуществляется в режимах Auto Halt, Quick Start, Deep Sleep и Deep Sleep Extended (DSX).

Технология LongRun версий 1 и 2, контролируемая CMS, позволяет динамически подстраивать напряжение питания ядра и тактовую частоту процессоров Efficeon, в зависимости от текущей программной нагрузки. Поскольку энергопотребление чипа имеет линейную зависимость от тактовой частоты и квадратичную от напряжения питания ядра, регулировка этих параметров, по заявлению представителей Transmeta, способна в отдельных случаях привести к обратной кубической зависимости энергопотребления.

Базой технологии управления энергопотреблением LongRun являются заложенные в CMS сценарии типичной загрузки системы различными программными приложениями. Изменения нагрузки детектируются и далее динамично используются для подстройки текущего режима процессора. Все подстройки энергопотребления прозрачны для операционной системы, контроллера энергопотребления и пользователя.

При активации технологии LongRun используется определенное количество контрольных точек подстройки тактовой частоты/напряжения ядра, позволяющие оптимизировать соотношение "минимальное энергопотребление/производительность" в рамках кривой на графике, приведенном ниже.

Изюминкой технологии LongRun2 является то, что транзисторы процессорного ядра "активизируются" при превышении определенного уровня напряжения на затворе – так называемого "Threshold Voltage", или Vt, обычно составляющего порядка 1/2 – 1/5 от напряжения питания. При минимальных значениях Vt транзисторы переключаются быстрее, однако, в этом случае относительно велики утечки тока. Напротив, при более высоких значениях Vt теряются мегагерцы, однако, снижаются токи утечки. Технология LongRun2 позволяет динамически подстраивать уровень Vt для оптимальной эффективности работы чипа, при этом полностью блокируются нежелательные флюктуации уровня Vt. В результате компанией объявлены следующие уровни рассеивания мощности ядра Efficeon в режиме Standby:

Рассеиваемая мощность при отключенном режиме LongRun2 – 144 мВт

Рассеиваемая мощность при включенном режиме LongRun2 – 2 мВт

Отдельно стоит отметить, что технология LongRun работает параллельно и в сочетании с ACPI. В моменты достижения минимальных значений тактовой частоты и напряжения питания ядра процессора на кривой LongRun, процессор автоматически возвращается к традиционным режимам управления энергопотребления, заложенным, например, в ACPI.

Что касается технологии управления терморежимом, LongRun Thermal Management, подразумеваются те же регулировки тактовой частоты/напряжения питания ядра, при этом утверждается, что LongRun в сравнении с обычными способами энергосбережения обеспечивает большую эффективность и производительность процессора при той же температуре или аналогичную производительность при меньшей температуре. На графике ниже приведены рабочие точки графика системы управления терморежимом процессора при использовании технологии LongRun.

В заключение приведу нагрузку 1 ГГц процессора TM8300/TM8800 в случае работы с типичными приложениями.

Заключение

Нельзя сказать, что собранные и изложенные в этой заметке данные проливают достаточный свет на внутреннее строение и принципы функционирования чипа Efficeon. Возможно, в этом – мой недосмотр и слабая подготовка к написанию материалов, возможно, виной этому в какой-то степени недостаточное освещение строения процессоров самой компанией Transmeta. В любом случае, надеюсь, что для первого взгляда этих материалов будет достаточно, а дополнительные подробности можно будет добавить позже, по мере появления информации...

Литература

- Материалы сайта компании Transmeta

- Материалы сайта PC Watch